【摘要】 本文介绍了一个应用于DRAM芯片的延迟时间稳定的时钟树驱动电路。所述的时钟树驱动电路采用一种随电压变化不敏感的驱动电路设计,以保证在驱动电路的供电电压发生过冲或者是有压降时,时钟树驱动电路的延迟时间能够保持相对稳定,从而保证输出数据时序稳定,实现较好的数据输出眼图。

【关键词】 时钟树 延迟时间 模拟集成电路

一、引言

随着JEDEC接口标准的不断升级,从最初的SDR到DDR,DDR2/DDR3,到目前最新的DDR4 接口协议, 动态内存芯片(DRAM)支持的时钟频率不断升高,DDR4 最高支持3200的数据传输速率。为了保证良好的数据输出眼图性能,DRAM中的时钟树电路设计变得非常关键。时钟树电路的时序稳定直接关系到DRAM输出数据眼图的大小。

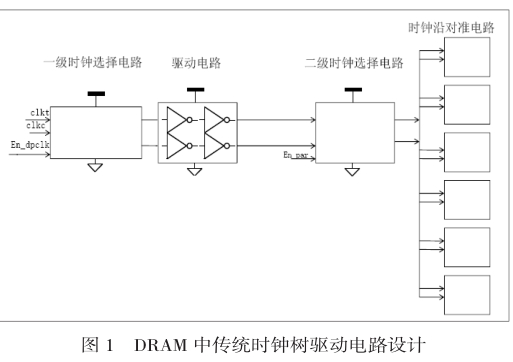

二、DRAM中传统的时钟驱动树电路设计

DRAM中的数字时钟锁相环输出的时钟信号需要经过时钟树驱动电路和片上输出驱动最终输出数据。而时钟树驱动电路部分的设计尤其关键。图1为一个目前DRAM中传统的时钟树驱动电路。Clkt,clkc为锁相环输出的互补时钟信号,en_dplck为一级时钟选通信号,en_par为二级时钟选通信号。由于时钟树驱动电路耗电较大,加上其一级时钟选择电路和二级时钟选择电路的使能信号随不同的操作模式进行开关切换,由此导致时钟树电路的耗电也会有动态的切换。

在DRAM芯片中,时钟树的供电电压由内部的LDO电压供电模块提供。一级时钟选择信号由与省电模式相关的信号生成,当芯片进入省电模式时,时钟树的时钟信号被关掉,耗电减少,电压会有瞬态的上冲;当退出省电模式时,时钟开启,耗电增大,内部供电电压有下降,由此会导致整个时钟树电路的传递延迟变慢,而且由于电压抖动对时钟信号的上升沿和下降沿部分的影响不同,也会导致时钟树电路的输出信号的占空比变差。而在目前的DRAM设计中,大多是通过增加供电电压网络上的电容或者改善供电电压生成器的性能来减少电压抖动,以期望改善时钟树输出信号的性能。但是这些方法占用了很大的芯片面积而且效果不是很理想。

三、DRAM中一种延迟时间稳定的时钟树驱动电路

为了解决现有的时钟树驱动电路在供电电压抖动时会产生延迟,造成输出数据眼图变窄的技术问题,本文所述时钟树驱动电路采用一种随电压变化不敏感的驱动电路设计,以保证在驱动电路的供电电压发生过冲或者是有压降时,时钟树驱动电路的延迟时间能够保持相对稳定,从而保证输出数据时序稳定,实现较好的数据输出眼图。

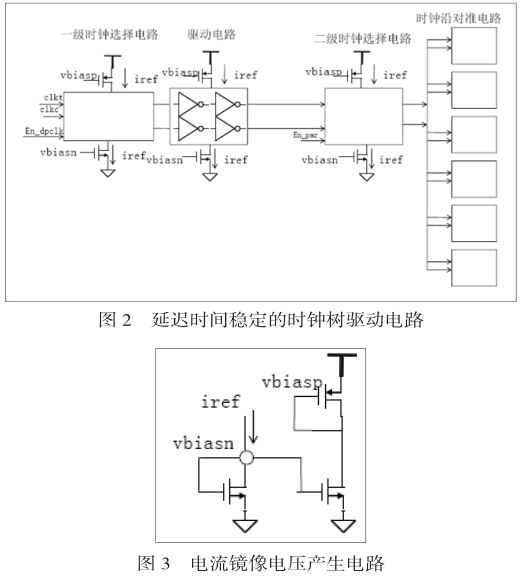

如图2所示,本时钟树驱动电路主要包括四部分电路:一级时钟选择电路,驱动电路,二级时钟选择电路,时钟沿对准电路,以及电流镜像电路。一级时钟选择电路上还连接有NMOS管和PMOS管,NMOS管和PMOS管的漏端均与一级时钟选择电路连接;驱动电路上连接有NMOS管和PMOS管,NMOS管和PMOS管的漏端均与驱动电连接;二级时钟选择电路上连接NMOS管和PMOS管,NMOS管和PMOS管的漏端均与二级时钟选择电路连接;

其中clkt,clkc为从数字时钟锁相环输出的一组互补时钟信号。En_dpclk为一级时钟使能信号,主要与省电模式操作相关。En_par为二级时钟使能信号,主要与读操作命令有关。Iref为DRAM芯片中与温度电压基本无关的参考电流。经过电流镜像电路生成vbiasn和vbiasp两个电压,分别连接到NMOS和PMOS的栅端镜像一个固定的电流到时钟树电路中。图3所示电流镜像电路的结构图。当然除了电流镜像电路,还可以是其他现有技术中一些能够产生电压的电路。

对于输入时钟信号clkt,clkc,当信号从低变高时,经过PMOS管精确镜像过来的电流Iref对内部节点进行充电,其充电时间固定,无论供电电压抖动大小,此时钟信号的上升沿和延迟时间都仅有Iref决定,同理,当信号由高变低时,经过NMOS管镜像过来的电流Iref对内部电压节点进行放电,其放电时间也不随供电电压变化,所以时钟信号的下降沿和延迟时间也都相对稳定。时钟树电路的每一级均经过上述处理后,那么整个时钟树电路的延迟时间和输出时钟的占空比都会对供电电压不敏感,从而保证了较好的输出数据眼图。此固定电流通过PMOS管和NMOS管对中间节点进行充电/放电,其充电/放电时间基本保持恒定。所以每一级电路的传递延迟仅与iref有关,与内部供电电压的抖动基本无关。

本文所述的延迟时间稳定的时钟树驱动电路,具有以下优点:

1、在时钟树驱动电路的设计中,采用一种随电压变化不敏感的驱动电路设计,以保证在驱动电路的供电电压发生过冲或者是有压降时,时钟树驱动电路的延迟时间能够保持相对稳定,从而保证输出时钟信号稳定,实现较好的数据输出眼图。2、本文所述电路结构设计简单,但却大大改善了电路的性能。

四、结论

通过采用一种随电压变化不敏感的时钟树驱动电路设计,以保证在驱动电路的供电电压发生过冲或者是有压降时,时钟树驱动电路的延迟时间和时钟的占空比能够保持相对稳定,从而保证输出数据时序稳定,实现较好的数据输出眼图。

参 考 文 献

[1]贾雪绒,“一种延迟时间稳定的时钟树驱动电路”专利号201420575679.2,证书号4086328;授权日期 2015/01/21

- 电视生活服务类节目创新的经济与商业探究

- 马斯洛需求层次理论浅析

- 我国海洋渔业资源如何走出“公地悲剧”

- 新疆医联体模式管理及其发展的相关思考

- 社会办医的新时期:机遇、挑战与策略

- 农村小学生心理健康教育探析

- 图纸档案电子化管理探析

- 新时期我国事业单位人事制度改革问题分析

- 事业单位间划拨用地无偿划转流程分析及建议

- 编室副主任提高业务管理的三大要诀

- 肇庆市引进高层次人才对策的研究

- “互联网+”背景下的社区治理模式探析

- 工会维权乏力原因及破解路径

- 政府职能市场化的现存问题以及解决方案

- 从传统管理思想中探析全面管理观

- 制造业企业销售与收款业务的内部控制分析

- BSC绩效考核在高新企业中的实施

- 基层党建与中心工作深度融合的研究

- 国有企业人力资源管理改革建议

- 少数民族聚居区实行差别化扶持政策的思考

- 白茶经济产业发展现状与对策建议

- 乡村振兴背景下新乡贤作用与建设研究

- 机关单位能力内耗的机理表现及改善之策

- 业财融合一体化内部控制管理新模式

- 实现中华民族伟大复兴的战略指引思考

- foreleg

- forelegs

- forelend

- forelie

- forelift

- forelimb

- forelive

- foreloader

- foreman

- foremanship

- foremanships

- foremean

- foremen

- foremention

- foremost

- foremostly

- forename

- forenames

- forensic

- forensic accountant

- forensicaccounting

- forensicalities

- forensicality

- forensically

- forensics

- 小别

- 小别数日

- 小前提

- 小前驼

- 小剧场

- 小力笨儿

- 小功

- 小功劳

- 小功近利

- 小加九儿

- 小动作

- 小动物的叫声

- 小劫

- 小劫红羊

- 小劲

- 小勿像猫,大勿像狗

- 小包工

- 小化

- 小化肥

- 小区

- 小千世界

- 小升不可以盛石,小智不可以谋大

- 小升初

- 小半

- 小半大儿