赵珊珊

摘要:PCI-Express是被应用广泛的串行总线和接口标准,为所连接的设备分配独享通道和带宽,具有高宽带和高速率的特点。本设计实现了PC与FPGA之间的高速通信,利用DMA控制数据传输,CPU仅在数据传输开始和结束时做处理,在传输过程中CPU可以进行其它工作,大大提高了CPU的利用率。通过板级测试表明,传输速率可达1.6GB/s。

关键词:PCI-Express 總线;FPGA;DMA

中图分类号:TP393 文献标识码:A 文章编号:1009-3044(2017)04-0032-02

卫星、无人机等对通信数据率的要求越来越高,且数据链传输距离长、信道环境复杂,因此极易受到干扰导致数据无法正常传输,或被截获泄露机密信息。自适应通信系统的通信体制、通信数据率、通信频点不再是固定不变的,能最大程度的躲避干扰,降低通信误码率。

传统的通信系统中,信号数据的处理通常在系统中设置一块数据处理板,用于完成频谱感知、调制模式识别等工作,但是板卡的数据处理速度和能力都有限,可能会降低系统的准确度和效率。PCIe在高速数据采集和传输系统中具有显著的优越性,本文设计实现基于PCIE总线的自适应通信系统数据处理系统,实现FPGA板卡与PC之间的通信,满足高速实时采集、处理和传输数据的要求,自适应系统调制模式识别正确率,频谱感知响应时间等指标。

1 PCIE总线简介

相比于以前PCI总线使用的并行结构(在同一条总线上的所有外部设备共享总线带宽),PCIE总线使用了高速差分总线。与单端并行信号相比,高速差分信号可以使用更高的时钟频率,从而使用更少的信号线,完成之前需要许多单端并行数据信号才能达到的总线带宽。在今后的通信领域中,使用高速差分总线代替并行总线是必然的。

PCIE使用高速差分总线,并采用端到端的连接方式,所以在每一条PCIE链路中只能连接两个设备。这使得PCIE与PCI的结构有所不同:

(1) PCIE采用的是串行数据数据包(TLP)的形式传输,在每层的数据及指令传输都以TLP数据包的形式,保障了数据传输的完整性和可靠性。

(2) PCIE在数据传输中,采用差分LVDS串行传输方式,一条PCIE通道由两对LVDS差分信号线来实现发送和接收。

(3) 采用了点对点串行连接,比起PCI总线的共享并行架构,能够为系统内的所有设备分配独立的通道资源,充分保障设备的带宽,提高数据的传输效率。

(4) 一个PCIE物理的连接可按照实际需要配置单通道,几通道或多通道(例如x1,x2,x4,x32)的链路模式,比PCI总线具有更好的灵活性。

相比于PCI,PCI-Express具有更好的系统架构及传输性能,所以PCIE取代PCI并行总线是大势所趋。而DMA在PCIE总线的应用更突显了PCIE的高带宽的优势,在高速DMA控制器传输方式下,对CPU仅占用了少许的资源,就能完成数据的高速端对端传输,因此具有广阔的应用前景。本设计针对此情景,提出了DMA参与控制的PCIE高速数据传输系统设计。

2 基于FPGA IP 硬核的PCIE接口设计

本系统设计采用是Xilinx公司Virtex-6系列的FPGA,板卡为ml605,芯片为xc6v1x240t,集成了Xilinx公司的PCIE官方IP硬核,该IP core遵循V2.0标准。PCIE接口采用模块化设计方法,首先使用Core Generation生成PCIE的硬核部分,链路宽度支持x1,x2,x4,x8四种模式。生成核的过程中需要配置各种参数,主要有:对应的Xilinx的开发板,TLP的大小,基址寄存器,设备ID,参考时钟以及链路宽度等。本设计使用的PCIE IP core提供6个32bit基地址寄存器BAR0~BAR5,可以根据用户设计需求进行配置。本设计中使用BAR0作为IO基址空间,使用BAR1和BAR2分别作为32bit内存操作基址空间。外部时钟输入频率100MHz,经过锁相环倍频125M后作为PCIE操作的全局时钟。

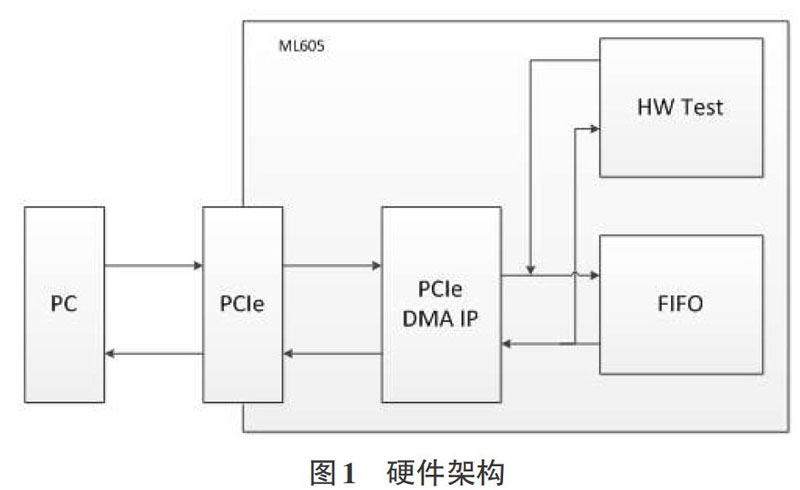

该硬核模块完成了数据高速串行与并行的转换,整个硬件架构框图如图1所示,PC与FPGA之间通信通过PCIE通道,靠DMA来控制,通过PCIE传输数据时,只需要占用很少CPU资源,CPU通过指令控制DMA,DMA自动控制数据的上传和下传,效率高且占用资源少。HW Test和FIFO为两种数据传输方式:HW Test(从FPGAPC)模式下从FPGA用户激励模块产生数据,再通过PCIE DMA上传,然后PCIE DMA回环下传,最后由FPGA激励模块接收数据并对比的功能;以及FIFO MODE(PCFPGA)下从PC产生数据,经过PCIE DMA下传,存进FPGA板上FIFO缓存中,数据再由PCIE DMA上传,最后PC接收数据并对比的功能。

此接口主要实现了解析IP核传输的数据包(TLP)信息并根据数据包的内容完成对应的读写操作等功能。实际使用时,用户可以直接使用PCIE的外部接口进行操作。

3 DMA控制器的实现

DMA(Direct Memory Access,直接内存存取) 是所有现代电脑的重要特色,它允许不同速度的硬件装置来沟通,而不需要依赖于 CPU 的大量中断负载。否则,CPU 需要从来源把每一片段的资料复制到暂存器,然后把它们再次写回到新的地方。在这个时间中,CPU 对于其他的工作来说就无法使用。在PCIE IP core基础上引入了控制器,数据的传输不再占用CPU的时间,提高了系统的运行效率。本节主要介绍PCIE接口的DMA读写操作核心设计。

3.1 DMA的接口设计

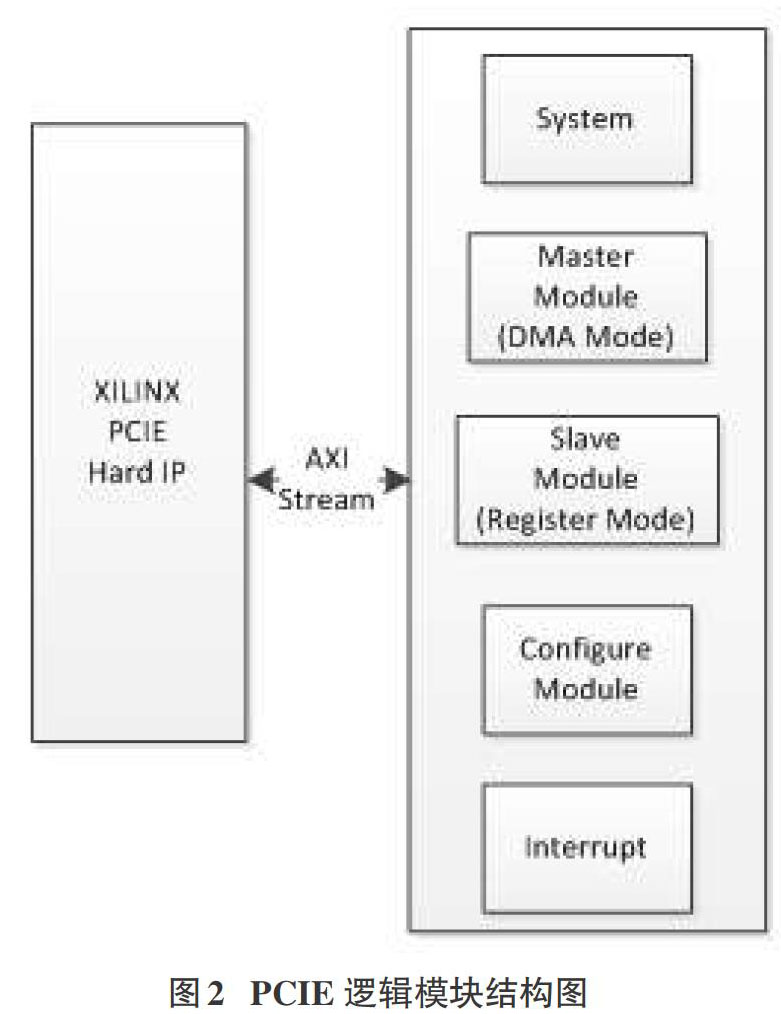

DMA控制器与PCIE IP core的接口设计主要分为DMA核心控制模块(DMA MODE)以及寄存器模块(register mode)和配置模块(configure)以及中断部分(interrupt)如图2所示。

3.2 DMA控制器

在整个设计中,DMA控制状态机是核心部分,主要包括TX Engine和RX Engine。TX Engine负责接收上位机存储器读写操作,单字发送及DMA發送。RX Engine主要负责存储器读写操作,单字接收及DMA接收。PCIE的DMA读写操作实现的主要方法是正确填写数据包头中的各个字段,并将数据按照64bit并行放在TLP包头中。对面DMA写,将数据传输给PCIE硬核,由硬核将数据发送到物理端口,最后传输到PC机的物理地址中;对面DMA读,主机将数据包发送到硬核,最后RX Engine解包,然后将数据输出。

PCIE DMA控制模块完成的主要功能:

1) 接收PC下发的PIO读写TLP请求,完成Bar空间寄存器的解码与回传工作。

2) 根据Bar空间解码,获取存储器写触发,完成产生存储器写TLP以及通过PCIe发送请求的功能。

3) 根据Bar空间解码,获取存储器读触发,完成产生存储器读TLP以及按序接收PC回复的完成报文数据的存储功能。

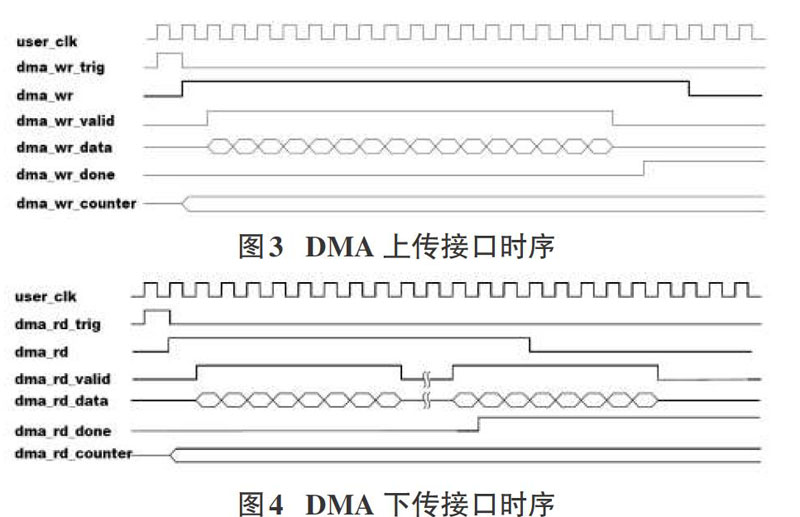

3.3 DMA上传下传工作时序

DMA读写流程如下:

(1)DMA写操作(数据从板卡搬移到PC内存)的控制流程如下:

PC申请一段物理地址连续的内存空间,并将其锁住防止其他程序占用;

PC配置DMA写寄存器,写入内存空间起始地址、TLP的有效数据载荷数、TLP的个数等,然后启动DMA事务;

FPGA上的Tx_fifo数据达到一定规模后,DMA Engine主动组织Memory Write TLP并通过PCIE核发至PC。DMA控制器会自动填充TLP包逐一增加地址信息,直到达到驱动程序设置的长度,最后DMA向PC发送MSI写中断;

PC接收到中断信号后,访问DMA的中断状态寄存器判断中断类型,如果是DMA写中断,则进入中断处理函数中。PC将这段物理地址的数据拷贝到用户空间,做处理,然后回步骤,同时在PC机上调用识别函数,识别算法完成后,将结果通过写寄存器的方式发送给下位机。

(2)DMA读操作(数据从PC内存搬移到板卡)的控制流程与写操作类似,不再赘述。

4 系统测试与分析

在完成代码的编写及各个模块设计之后,用modelsim对程序进行仿真。使用Xilinx公司的ML605实验平台设计完成,FPGA程序使用Verilog HDL语言编写,编写环境是ISE(Integrated Software Environment)14.7,硬件测试时使用Chipscope抓取数据,主要分析上传到PC内存的数据与FPGA段发送的数据是否一致以及DMA控制器产生的PCIE总线传输信号时序是否满足要求。整个传输过程由上位机软件控制,负责发起和结束控制,规定传输数据的内容。

本设计一次DMA读写操作的包长均为64字节,基于PCIe接口的DMA传输实现了对数据的连续读写操作,DMA方式工作正常。读写过程中,上位机和下位机之间持续通信,连续读或写数据根读写的总数据量和总操作时间,计算出DMA读写 (下转第36页)

方式下的传输速率。经测试,该PCIe接口板DMA读模式下,数据传输速率可达1647.2MB/s,DMA写模式下,数据传输速率可达1605.3MB/s,PCIe接口板具有明显优势。测试上位机软件如图5所示。

5 结论

本文提供了一种基于PCIE IP 硬核的高速DMA数据传输系统设计,使得传输数据速度大幅度提高,且占用的CPU资源少。经过实际测试,本设计系统的数据传输速度在1.5GB/S左右,完全可以满足工作需要。为高速数据采集存储方面提供了一种通用的解决方案,具有很好的参考和应用价值。

参考文献:

[1] 王齐.PCI Express 体系结构导读[M].北京:机械工业出版社,2010.

[2] 雷雨,任国强,孙健等.基于PCIE 的高速光纤图像实时采集系统设计[J].电子技术应用.2013,39(10):136-142.

[3] 魏芸.基于FPGA的PCIe总线DMA平台设计[D].武汉:武汉理工大学,2013.

- 如何促进我国精神文明建设

- 临朐嵩山生态旅游区乡村旅游产品开发研究

- 基于开放性思维的初中英语教学改革模式探讨

- 《实用翻译技巧》微课教学方式改革探究

- 内蒙古沙漠旅游资源探索与研究

- 黄冈市观鸟旅游开发的SWOT分析及对策建议

- 基于旅游动机的旅游者聚类研究

- 大湘西旅游圈智慧旅游发展的动力机制研究

- 农村乡风存在的主要问题

- 徐州市旅游业发展现状分析

- 全域旅游视角下浙东唐诗之路的旅游开发研究

- 桂林古东瀑布旅游景区生态建设

- 网媒对培养高校学生媒介素养功能研究

- 万宁旅游核心竞争力产品打造分析研究

- The Determining Factors of Economic Development

- 优化旅游生产要素下的广西乡村贫困地区旅游精准扶贫思考

- 南京非物质文化遗产保护现状与发展对策

- 符号消费理论视野下的家庭旅馆经营主体变迁研究

- 新时代武装保卫人员思想政治工作探究

- 基于学生视角下的校园欺凌现状分析

- 吉林省入境旅游市场发展研究

- 基于图式理论指导的高职英语听力教学策略研究

- 关于江门市“产城融合”的研究

- 双院制下大学生党员培养和管理初探

- 十堰市智慧旅游公共服务体系建设研究

- initialprice

- initial public offering

- initialpublicoffering

- initials

- initialyield

- initial²

- initial³

- initial¹

- initiate

- initiated

- initiates

- initiate sb into

- initiating

- initiation

- initiations

- initiative

- initiatively

- initiatives

- initiators

- in its entirety

- inject

- injectables

- injected

- injecting

- injection

- 一只螃蟹八只脚

- 一只蠓虫儿飞过去,也能分出公母

- 一只角

- 一只针没有两头利

- 一只飞蚊从眼前掠过,也能分出公母

- 一只骆驼上的两只驼峰——谁也离不开谁

- 一只鼎

- 一只鼓不能敲两家戏

- 一召唤就来

- 一可当十

- 一台二妙

- 一台二绝

- 一台戏

- 一台车床

- 一台锣鼓半台戏

- 一叶

- 一叶两豆

- 一叶惊寒

- 一叶惊秋

- 一叶扁舟

- 一叶报秋

- 一叶浮萍归大海,为人何处不相逢

- 一叶浮萍归大海,人生何处不相逢

- 一叶浮萍归大海,人生何处不相逢。

- 一叶知秋