摘 要:针对深亚微米工艺下后端实现中布线资源紧缺这一难点提出了一种改进的层次化流程.通过考虑子电路在上层电路中的连接关系调整子电路的高宽从而优化布线资源并降低延迟.采用量化分析的方法一次性得到可实现的物理设计,避免了多次迭代尝试浪费的时间.以DSP中大规模多路选择器在SMIC 65nm low leakage工艺下的物理设计为例介绍了本文提出的优化方案,并且对比可得本文提出的方法能减少20%的面积和35%的延迟.

关键词:版图;延迟;高速;面积;布局

中图分类号:TN431.2 文献标志码:A

Abstract:This paper proposed an improved hierarchical flow for physical design in deep submicron technology. This flow can reduce routing congestion and improve timing delay. The key point of this flow is to use the external connectivity information of the target block to design the floorplan, which could achieve a good place and route result in one iteration using quantitative analysis, saving time and efforts from multiple failed iterations. The proposed flow was tested on a large mux block in DSP design in SMIC 65 nm low leakage process, and the result showed it improved 20% in area and 35% in timing delay compared with the traditional flow.

Key words:layout; delay; high speed; area; placement

隨着集成电路技术的发展,芯片的规模以及工作频率在不断提高,并且使得芯片物理设计所用的EDA工具面临更多的挑战,其中以Routing congestion(布线堵塞)最为突出.关于后端设计的流程和挑战已有不少研究[1-4].

随着工艺节点的缩小,标准单元的长宽和金属线的间距(pitch)按相似的比例缩小,因此标准单元的面积缩小的倍数约等于金属线间距缩小的倍数的平方.随着工艺尺寸的缩小,单位面积内的单元增加的速度将远大于布线资源增加的速度,同时工艺尺寸的缩小也会使一些原来可以忽略的效应变得更加明显,需要考虑更多约束[5-8],导致深亚微米工艺中布线将消耗更多的布线资源,因此很可能出现布线资源不够用即布线堵塞现象.

传统的物理设计流程将所有的网表文件同时读入并进行布局布线等操作,本文将此种方式称为扁平化物理设计,以区分于后文所说的层次化物理设计.

随着电路规模的增大,电路的连接复杂度将显著增加.对于超大规模电路,使用扁平化物理设计会导致需要的计算量和内储资源显著增加,受限于当前计算机运算的运算速度和内存,进行物理设计所需的时间同样将显著增加,并且通常无法获得较优化的布局布线结果,需要占用更多的面积来进行布线,导致面积利用率(逻辑门所占的面积/总面积)下降.本文以一个10万门的模块和一个100万门的模块为范例进行比较,比较结果如表1所示.

因此目前对于大规模电路,一般采用层次化后端流程:将复杂电路划分成多个子模块,对各自模块分别进行物理设计,上层电路进行物理设计时调用已完成的下层模块.层次化物理设计的优点是可以避免物理设计过程中载入大规模电路,从而可在较短的时间内得到一个较优化的布局布线结果.此外将某些逻辑关系复杂并且不会再改动的模块划分为子模块也能避免由于其他电路的改动而要重新对整个电路进行物理设计,节省时间.但是如何划分子模块以及如何设定子模块的长、宽和端口位置目前没有具体的理论和分析.

本文在一般层次化设计流程的基础上进行定量理论分析,将进行层次化物理设计模块在上层电路中相关的连接关系加入考虑范围,通过公式计算出子模块的最小长宽需求和端口位置.避免了靠感觉选定模块参数然后反复尝试造成的设计时间浪费.本文将以上千位宽的多路选择器为例描述新流程并将与传统流程进行对比.

1 优化层次化物理设计

1.1 自动化工具的缺陷

对于层次化设计,EDA工具并不会对子模块的高宽以及端口位置提出有意义的推荐设置.目前也没有公认的流程来确定子模块的高宽等约束,因此传统流程中子模块的高宽全凭设计者个人的经验和感觉.以多位选择器为例,其最小的子模块面积约为1 201 μm2,EDA工具自动优化的结果是其高宽比将趋于1∶1,即被设定为约34.6 μm.其纵向端口以及从其上穿过的其他子模块的纵向端口连线总共有348,由于总共只有8层金属,因此需要禁止子模块使用第7层及以上的金属层,同时子模块内部走线需要用到第2层金属,因此其穿过模块的纵向连线只能使用第6层金属和第4层金属.假设第4层和第6层的布线资源全用来连接端口连线,由于每层金属的pitch为0.2 μm,34.6 μm的宽度最多通过346个端口连线.因此EDA工具自动给出的布局方案将无法完成布线.

传统流程中,若物理设计无法实现则会增大面积再试一遍,直到成功为止.本文提出的优化方案能提供一个具体的流程量化分析所需高宽的最小值,避免盲目增加模块面积并且节约多次迭代所需要的时间.

在电路设计过程中某些特定的逻辑模块会被重复使用多次,这种情况下可以将被多次调用的逻辑模块作为子模块进行物理设计以节约整体物理设计的耗时,并且如果这些子模块互相之间也有复杂的连接关系还可以将包含这些复杂的连接关系的多个模块整体再视为一个新的子模块,使得EDA工具可以单独优化这一特殊复杂模块的延迟和面积,避免其他部分电路改动对此复杂模块的影响.

1.2 计算子模块高宽

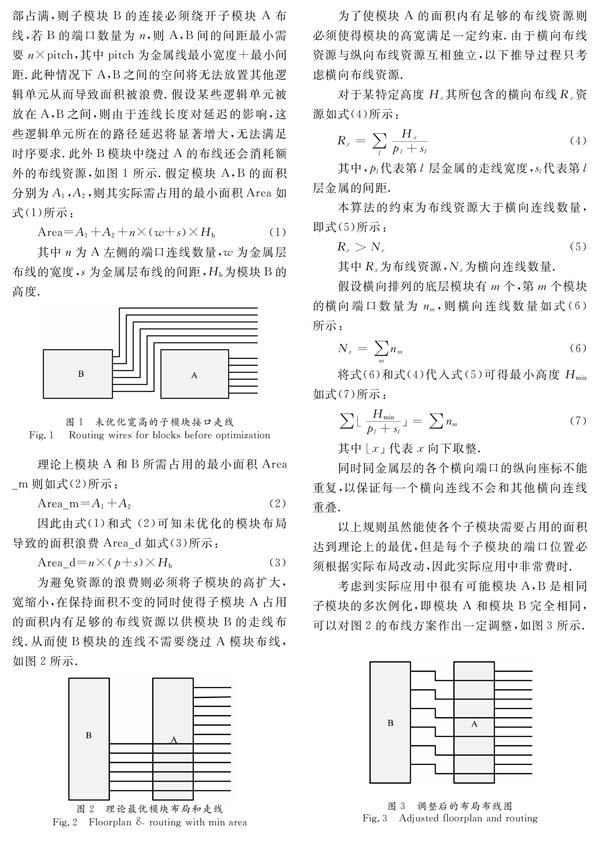

为了方便说明,本文将包含有其他子模块的子模块称为中层子模块,而不包含子模块的子模块称为底层子模块.通常底层子模块和中层子模块会定下禁止第X层金属布线的规则以给顶层连线预留布线资源.如果制作底层子模块时没有考虑其被调用时的连接关系则会出现如下问题:

1.3 优化跨模块连线

当多单个子模块的宽高较大或者多个子模块放置在一起时,虽然子模块本身没有禁止布线从其中穿过但是依旧会因为其他约束造成布线无法从其中穿过.

原因之一是当连线长度增加时其负载也会增加,从而造成延迟时间翻转时间变长,最终超过约束中最大限制造成违例,通常工具将试图插入缓冲器来解决这一违例,但是由于已完成的子模块内无法再放置新的单元,因而导致这一违例无法修复.此外连线过长还会产生串扰,天线效应等问题,通常工具都会试图通过插入缓冲器来解决,但同样也无法实现.因此连线只能绕过此子模块.如图4所示,B是一个宽度W较大的子模块,线n1从B左侧的A连到B右侧的C,由于n1连线较长需要插入缓冲器,由于缓冲器只能放在B以外的位置, n1只能绕过B布线而不能穿过B.

因此占用面积较大的子模块会禁止连线从其内部穿过,导致其占用面积上的很大一部分的布线资源被浪费.并且当需要从子模块B上穿过的线比较多时,这些连线会集中在模块B边缘,导致子模块B附近的布线资源过于拥堵,影响后端实现.

为了避免布线资源的浪费我们可以在对B模块进行物理设计时预先留出对应的通道接口(feedthrough ports),将需要穿过子模块B的线全部设计成子模块B内部的连线.这样在使用子模块B的时候只需要将线连到子模块B的接口即可,如图5所示.图5中虚线方框为制作B模块时预先加入的缓冲器,因此A和C直接接到B模块的通道接口并不会由于连线过长产生违例.

实际应用中有可能类似于n1的需要穿过子模块B的连线太多无法全部设置为通道.这种情况下我们可以在对模块B进行物理设计时将其边框“挖除”一些空位来让工具在上层进行物理设计时可以在被挖出的空间内插入所需的缓冲器.

2 对比结果

本文中以多核DSP中的多位选择器模块为例,此多位选择器结构图如图6所示.

32个如图所示的单数据位选择器构成一个通道,整个多路选择器由8个通道构成,各通道共用相同的70个32位的数据输入,但是每个通道有各自独立的选择信号.此模块总共有70×32+(7+6+5+5+3+5) ×32×8=10 176个端口,其规模为10万逻辑门数量级.由于其内部有较多的连线,若直接按传统层次化流程,按经验设定70%的面积利用率则会因为布线资源问题无法完成物理设计.通过不断尝试增加面积的多次迭代尝试最终能完成此模块的物理设计,其面积为0.436 mm2,延迟为2.3 ns.

若采用本文提出的方案,将单数据位模块定为底层模块,并且将数据输出规划为横向连线,数据输入规划为纵向连线,则每个通道内单数据位模块只能横向排列以避免不同数据位的输入纵向连线过于密集.而各通道将按纵向排列从而使得不同通道内同数据位的子模块可以共用同一个纵向连线作为数据输入,最大化减少同一个逻辑线的分叉连线,节约布线资源.此种布局规划下对于底层子模块其纵向连线为348个,其横向连线为80个,纵向可用金属为第2,4两层,横向可用金属为第3层,各金属层布线宽度为0.1 μm,间距也为0.1 μm.将纵向和横向数据分别代入公式(7)可算出其最小宽度需要至少34.8 μm,其最小高度需要至少16 μm,考虑到最小高宽所得到的面积小于模块面积,因此本文将高宽增加相同的余量,使其面积利用率达到70%,即高宽各增加约10 μm,最终宽为46.6 μm,高为25.2 μm.

考虑到底层子模块连线的长度较长,在对上层子模块进行物理设计时,调用底层模块的同时规模其摆放位置,使每个子模块与其他子模块相隔一个缓冲器的距离.同时考虑到纵向连线较长,修改上层子模块的网表文件,为所有的纵向端口连线手动增加一个缓冲器并约束其位置于整个子模块中间.

由于各个子模块的规模很小,工具可以对每个子模块进行较好的优化处理,最终完成的物理设计会比传统流程有很大的提高.新流程得到的物理设计面积减少约0.357 mm2,速度减少为1.5 ns.本文提出的优化方案得到面积约是优化前的80%,延迟约是优化前的65%.优化后的版图如图7所示(为了便于查看,已将连线隐藏).理论上通过式(3)得出的可节约的面积约为0.028 67 mm2,而实際上节约的面积为0.079 mm2.多节约的面积是因为本模块的规模和复杂度过大,物理设计工具无法获得最优解.由于传统流程无法达到最优解,导致传统流程所得延迟同样较差,此外传统流程造成的多余面积会造成连线长度增加,导致连线负载增加,最终导致传统流程的延迟与本文提出的流程相差35%.

3 结 论

本文针对一般的层次化流程的不足提出了相应的改进方案,考量自动布局布线的缺点,通过考虑上层电路的连接关系详细规划子模块的布局和端口约束,提出量化公式指导子模块的高宽及端口约束,降低面积和布线资源的浪费,避免多次失败的物理设计迭代,并使得每个子模块规模较小,避免工具无法优化的情况出现,以达到较小的面积和延迟.以DSP中多位选择器为例,成功减少电路约20%的面积和35%的延迟.

参考文献

[1] SHARMA T, STEVENS K S. Physical design variation in relative timed asynchronous circuits [C]//IEEE Computer Society Annual Symposium on VLSI. Piscataway, NJ: IEEE, 2017: 278-283.

[2] GUPTA A, RAWAT K, PANDEY S, et al. Physical design implementation of 32bit AMBA ASB APB module with improved performance [C]//International Conference on Electrical, Electronics, and Optimization Techniques. Piscataway, NJ: IEEE, 2016:3121-3124.

[3] SHAM C W, YOUNG E F Y, LU J W. Congestion prediction in early stages of physical design [J]. ACM Transactions on Design Automation of Electronic Systems, 2009, 14(1): 12:1-12:8.

[4] 曾宏. 深亞微米下芯片后端物理设计方法学研究[J]. 中国集成电路,2010,19(2): 30-35, 49.

ZENG H. IC Physical design methodology research under DSM [J]. China Integrated Circuit, 2010, 19(2): 30-35,49.(In Chinese)

[5] SHIM S, CHUNG W, SHIN Y. Lithography defect probability and its application to physical design optimization [J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2017, 25(1): 271-285.

[6] LIU M, SUN W Q, WANG W Q, et al. An automatic and practical flow for clock tree construction in physical design [C]//7th IEEE International Conference on Software Engineering and Service Science. Piscataway, NJ: IEEE, 2016:671-674.

[7] NASSIF S R, NAM G J, BANERJEE S. Wire delay variability in nanoscale technology and its impact on physical design [C]//14th International Symposium on Quality Electronic Design. Piscataway, NJ: IEEE, 2013:591-596.

[8] THIELE M, BIGALKE S, LIENIG JENS. Exploring the use of the finite element method for electromigration analysis in future physical design [C]//IEEE International Conference on Very Large Scale Integration. Piscataway, NJ: IEEE, 2017: 1-6.

- 公共图书馆提升服务效能的途径

- 解析大数据时代公共图书馆图书资料管理

- 网络时代图书资料管理的新模式分析

- 基于泛在知识环境的国内外图书馆学科服务研究

- 高校图书馆编目员的职业倦怠研究

- 图书馆资源建设与新时代文化发展

- 医院信息化建设中图书馆的功能定位和发展策略论述

- 政采模式下高校图书馆纸质图书采访中的问题及应对措施

- 新时期高校图书馆面临的挑战和机遇

- 互联网时代下图书馆档案信息化管理创新

- 图书馆读者服务呼唤人文精神

- 网络环境下图书馆管理模式创新

- 数字出版环境下图书馆纸质图书采访面临的困境及路径选择

- 浅谈如何提高图书馆图书管理水平

- 高校图书馆读者服务创新研究

- 高校档案信息化管理安全策略探讨

- 公立医院人事档案信息化管理体系的建设和实践

- 浅析信息时代如何做好档案管理工作

- “互联网+”背景下电子档案与纸质档案融合的档案管理模式探析

- 信息时代如何做好电子档案安全管理

- 医疗卫生事业单位档案的信息化建设管理分析

- 基于“互联网+”的档案服务模式创新发展策略

- 试析行政档案管理中信息化技术的应用

- 信息化背景下的事业单位档案管理模式探讨

- 土地档案管理信息化建设的重要性与方法研究

- mealy-mouthed

- mealy mouthed

- mealy-mouthedly

- mealy-mouthedness

- mealy-mouthednesses

- mean

- mean a lot to

- mean business

- meander

- meandered

- meanderer

- meanderer's

- meanderers

- meandering

- meanderingly

- meanders

- meaner

- meaners

- meanest

- meaning

- meaningful

- meaning-fully

- meaningfully

- meaningfulness

- meaning-fulness

- r2013010010000087

- r2013010010000088

- r2013010010000089

- r2013010010000090

- r2013010010000092

- r2013010010000093

- r2013010010000094

- r2013010010000095

- r2013010010000096

- r2013010010000097

- r2013010010000098

- r2013010010000099

- r2013010010000100

- r2013010010000101

- r2013010010000102

- r2013010010000103

- r2013010010000104

- r2013010010000105

- r2013010010000107

- r2013010010000108

- r2013010010000109

- r2013010010000110

- r2013010010000111

- r2013010010000112

- r2013010010000113