卢绍英 王泽忠

摘要:平面埋阻技术可应用于高性能、高集成度的微波多层电路。随着微波产品小型化、轻量化需求的提高,平面埋阻技术得到了更广泛的应用。本文源于高低频混压板的功能需要,通过有限元法仿真设计了基于埋阻技术的单节功分器,利用ADS对功分器进行级联仿真,实现了S波段功分器的小型化设计。

关键词:平面埋阻技术;功分器;高低频混压板

中图分类号:TP311 文献标识码:A 文章编号:1009-3044(2017)18-0208-02

1概述

在高集成、多通道微波系统中,功分器是一种基础却又重要的元件。随着数字阵列模块(Digital Array Module)集成度的增高、体积和重量的减小,功分器也从一个独立的元器件,发展到了小型化的微波多层电路,集成到具有多种功能的高低频混压板中,成为集成化设计的一部分。

隔离电阻是功分器的重要元器件,其性能指标和装配方式直接影响驻波和隔离等指标。传统使用电阻器焊接的方式制约了多层功分器的集成,同时焊接时产生的分布参数也不一致,在功分器级联应用时,对性能指标产生了影响。平面埋阻技术是提高功分器集成度、满足级联一致性的有效手段。

本文通过三维电磁场分析软件HFSS仿真设计了基于埋阻技术的单节功分器,利用微波电路仿真设计软件ADS对功分器进行级联仿真,实现了基于平面埋阻技术的S波段功分器的设计。

2平面埋阻技术

平面埋阻技术主要有两种:

1)采用丝网印刷技术,将固定的电阻浆料刷印在板面,此方法电阻精度不高,有文献记载误差在10%;

2)采用含电阻层的薄膜材料,通过成像蚀刻的方式制成电阻,误差在8%左右。

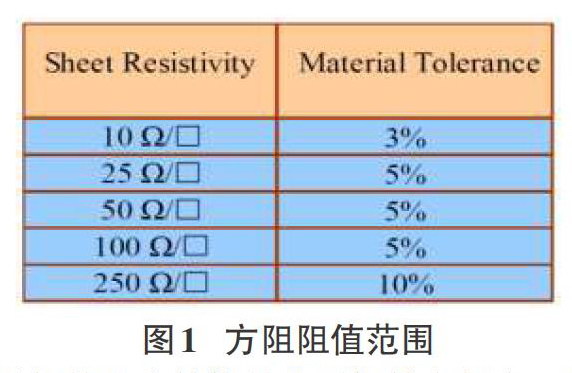

目前多层高频介质板通常选用薄膜材料Ohmega-ply获得比较精准的薄膜电阻。可提供的阻值范围是(25~250)Ω/□(图1所示),

高频介质板的基本结构是两层铜箔之间夹一层介质层,而带有Ohmega-ply材料的高频介质板是在铜箔与介质之间夹一薄层镍合金材料作为电阻层,其基本结构及实现方式见图2。

当需要使用方阻时,按设计图形,用蚀刻工艺将镍合金材料层上的铜箔蚀刻干净,即可形成铜端接镍电阻。

3 S波段功分器设计

Wilkinson功分器具有宽带宽、驻波小、结构对称的特点,便于级联设计,成为小功率功分器设计的首选。鉴于平面埋阻技术可提供较理想的埋阻形式,为减小体积,适应高低频混压板设计要求,本文采用带状线形式,设计了S波段八等分功分器。

为保证多层板层压可靠性,选用z轴膨胀系数较小的高频介质板CLTE-XT,厚度0.508mm,带埋阻的高频介质板选用CLTE-XT-50(方阻阻值50I]),厚度0.508mm,粘贴膜使用FAS-TRISE,基本结构见图3。

3.1单节功分器仿真

单节Wilkinson功分器通常使用奇-偶模分析的方法进行初步设计,得到理论参数,然后使用仿真工具建模优化。本文使用三维电磁场分析软件HFSS进行建模仿真,仿真模型见图4。其中电阻设置利用阻抗边界条件(Impedance),隔离电阻理论为10012,方阻阻值5012,故电阻图形长宽比设计为2:1,阻抗实部500hm,虚部0 Ohm。

经仿真优化,单节Wilkinson功分器端口驻波特性见图5,其中VSWR(1)表示总口驻波,VSWR(2)、VSWR(3)为分口驻波;插入损耗仿真见图6。

3.2八等分功分器仿真

鉴于HFSS建模及大尺寸仿真时间较长,通常S波功分器段级联仿真可使用微波电路仿真设计软件ADS,将单节Wilkin-son功分器S参数仿真结果导人,进行级联仿真。

经仿真优化,八等分功分器总口驻波见图7,分口驻波见图8,插人损耗仿真见图9,相邻分口隔离度见图10,仿真结果符合设计要求。

4结束语

本文所述的基于平面埋阻技术的S波段功分器實际指标测试结果:总口驻波小于1.35,插入损耗小于0.8dB,隔离度大于25dB。满足了高低频混压板的功能需要。

在工程实践中发现,由于埋阻材料的很脆弱,在图形处理及层压时铜端接镍电阻极易受到破坏,最终阻值精度不满足要求甚至造成电阻开路;另外目前基于平面埋阻技术的功分器设计还存在阻值精度不一致、多级级联阻值测试困难等问题,但随着国内印制板厂家工艺技术的提升,这些问题终将解决。

- 浅析数学解题的规范性

- 初中数学教学与信息技术多媒体的整合

- 对于学生接受定义的几点思考

- 小议初中数学教学中数形结合思想的应用

- 探究式教学在高中数学教学中的实践

- 基于矩阵分解的推荐系统在教学资源平台中的应用

- 浅谈系统论、信息论、控制论对数学教学的启示

- 城市用水量组合预测模型和应用策略研究

- 一类Riccati方程的可解的条件

- 整体思维在高等数学中的几点应用

- 基于数学建模活动的高校数学教学改革

- 农业院校“数值分析”实践教学改革研究

- HPM视角下“平行四边形的面积”教学设计启示

- 变换立体图形维度 深刻把握图形特征

- 初中数学数形结合思想教学研究与案例分析

- 透析问题解决策略,提高高三复习效率

- 小学数学计算能力培养探究

- 刍议多媒体教学手段优化小学数学教法的策略

- 培养小学生的数学学习习惯的方法

- 小学数学的有效教学的策略

- 差异性在小学数学课堂中的应用

- 基于核心素养的小学数学空间观念的培养

- 数学,让生活更精彩

- 小学数学生活化作业的创新设计分析

- 关于信息技术与小学数学教学的深度融合探讨

- colour-ˌcoded

- cols.

- cols

- col's

- colt

- colthood

- colting

- flout

- flouted

- flouter

- flouters

- flouting

- floutingly

- flouts

- flow

- flowabilities'

- flowabilities

- flowability

- flowability's

- flowable

- flowchart

- flow chart

- flow-chart's

- flow charts

- flow-diagram

- 拗分

- 拗别

- 拗劲

- 拗口

- 拗口不顺

- 拗口令

- 拗口,不流利

- 拗口,不顺口

- 拗强

- 拗得过

- 拗怒

- 拗性

- 拗戾

- 拗执

- 拗抗

- 拗折

- 拗拢

- 拗捩

- 拗掉

- 拗救

- 拗断

- 拗曲作直

- 拗格

- 拗气损财

- 拗犟