潘志平

触发器是时序逻辑电路的基本单元电路,在数字电路和计算机电路中具有重要的作用。根据触发器的逻辑功能不同,触发器可以分为RS、JK、D、T型触发器等。触发器波形的分析研究,是本文讨论的重点。如何快速准确地分析作图,笔者认为必须掌握以下几种不同情况下的波形画法。

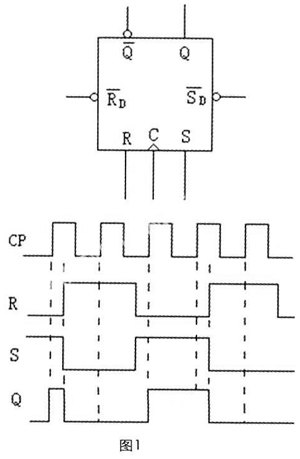

一、触发器的空翻现象

空翻是指对于钟控同步RS触发器当时钟脉冲宽度tp大于4倍的与非门(由与非门组成的钟控同步RS触发器)信号平均传输延迟时间tpd时,触发器将发生多次翻转,造成触发器的动作混乱。在RS、JK、D、T型触发器中,存在空翻现象的是钟控同步RS触发器,所以分析时对这类触发器要考虑其空翻现象。如图1所示是由与非门构成的钟控同步RS触发器,要求作出输出端Q的波形(设触发器初态为零)。此时,根据真值表作图时必须注意在CP=1期间如果R、S的状态发生变化,那么Q的状态也要随之改变。图中当第一个CP的上升沿到来时,R=0、S=1,根据真值表,Q要变为1,此时对于其它触发器这个逻辑1要保持到第二个CP的上升沿才考虑其变化,但对于钟控同步RS(由与非门组成)触发器,根据触发器的原理电路,在CP=1期间两个输入端所在的与非门是打开的,当R、S的状态发生变化时,只要时钟脉冲宽度tp大于4倍的与非门平均传输延迟时间,Q的状态也跟着变,即在第一个CP脉冲等于1期间R、S的状态分别由0、1变为1、0时,Q的状态应由1变为0(具体见图1)。

也就是在波形分析时不仅仅考虑CP脉冲到来这一时刻,还要注意CP=1期间R、S状态的变化。另外注意,根据电路原理的不同,对于或非门组成的钟控同步RS触发器要考虑的是CP=0期间R、S状态的变化。

二、存在级间连接线的多触发器电路

对于多个触发器构成的电路,要观察其是否存在相互间的连接线,即存在输出端Q或者 (符号与图中相对应为正体,全文下同)与输入端的连接线。此时,分析波形时要同步考虑,即Q、 及输入端的波形一起画,因为它们是相互关联的。如图2所示的电路中,存在两级间的连接线, 与2J相连,Q2与1K相连,则1J、1K、Q1、2J、2K、Q2要同步画。解题时首先将1J、1K、Q1、2J、2K、Q2按顺序从上到下依次排列,并将相连接的输入输出端在波形图中作好标示,如图中标出Q2=1K、 =2J。接着按照Q2→1K→Q1→2J→Q2的顺序同步作出,而不能独立作出Q1、Q2的波形。

三、脉冲上升沿和下降沿在时间上的前后控制

在两个触发器构成的电路中,如果用同一个CP的上升沿和下降沿分别控制两个触发器,则应按照CP到来的时间顺序分别作出。图2所示原理电路中,时钟脉冲CP的下降沿控制输出端Q1的状态,而CP经一个非门后再以下降沿控制Q2的状态,这时的Q2其实是由CP的上升沿来控制的。根据图2 所示的波形,CP首先出现的是上升沿,故应先作Q2的波形,然后是下降沿,即再作Q1的波形,这样根据CP上升沿下降沿到来的时间先后顺序,按照Q2→Q1→Q2……这样的循环顺序作出相应的波形,而不是按照 Q1→Q2→Q1……的顺序作出波形。这是解本类题的关键。

四、存在 、 控制的电路

是触发器的直接置0端和直接置1端。通常在时钟脉冲工作前使用,可将触发器直接置0或置1。但有时在题中加入了 或 的波形要求分析输出波形,此时根据触发器的原理电路,应注意 、 在每个触发器中靠输出端Q最近,只间隔一个与非门,而J、K、CP的状态变化需要经过多个与非门才到达Q端引起它的变化。一旦 、 为零则可直接将触发器置0或置1。此时不管CP还是J、K的状态如何,触发器的状态一定为0或者1。如图2中,当CP的第5个脉冲的上升沿来临时,2J=1,2K=1,根据JK触发器的真值表,Q2应由0翻转为1,但由于此时 =0,则触发器只能为零,一直等到 变为1后,再出现CP的上升沿时,才可以根据2J、2K的状态来确定Q2的状态,具体如图2所示。从这里可以看出,在存在 、 的波形控制电路中,确定输出端Q的波形时,首先看 、 ,接着是看CP,最后再根据输入端的状态由真值表来确定Q的状态。

五、组合逻辑电路与时序逻辑电路在波形分析时的区别

当组合逻辑电路与时序逻辑电路组合在同一电路中时,应注意它们的区别。组合逻辑电路是一种无记忆功能的电路,任一时刻的输出直接由当时的输入来决定,如图3中异或门的输出只由A与 的状态来决定,与CP无关。而触发器属于时序逻辑电路,它的输出不仅与CP有关,还与触发器的输入T原来的状态有关,作图时需区别对待。

六、CP脉冲的变化与输入端的状态的变化同时发生

图3所示波形中,当CP的第四个脉冲上升沿到来时,根据T=A作出波形,发现T的状态也正好由0态变为1态,此时确定Q的状态时是根据T=0还是T=1呢。根据T触发器的原理电路,T触发器是由JK触发器将J、K端相连而得到,而从T(即J、K端)状态的输入到输出Q的变化,需要经过多个与非门,即需要一定的传输延迟时间,所以,当第四个CP的上升沿一出现,经过一个非门后即将从触发器封锁,T=1的状态还来不及传输到Q端,所以应根据T=0来确定输出端Q的状态。

触发器电路千变万化,要正确分析触发器的输入、输出波形,就必须从电路原理着手,理解其实质,掌握以上这些关键点,才能轻松驾驭。

(作者单位:江苏省南通市中等专业学校)

- 浅谈初中生数学直觉思维能力的培养

- “把关”老师该“把”在哪?

- 历史故事在初中政治教学中的应用

- 试论提升高中生地理学习能力的对策探究

- 反思地理课改 探讨教学误区

- 将3D打印技术运用于高中地理教学

- 信息技术在高中地理教学中的应用调查研究

- 新形势如何提升高中地理教学的有效性研究

- 浅谈地理教学“自主学习合作探究”能力的培养

- “口误”:地理课堂教学中的硬伤

- 循循善诱,回归历史课堂趣味性

- 教研组建设与特色教研体系的建构思考

- 初中历史互动性教学的策略

- 高中历史探究式教学初探

- 基于学科教学知识的高中历史教师成长探析

- 初中历史课堂教学内容拓展微探

- 初中历史教学中学生学习兴趣的有效培养策略

- 从情感态度价值观谈体验式教育在历史教学上的运用

- 试论高中历史课堂培养学生思维能力的对策

- 初中历史试卷讲评课中的非生态现象及生态设计

- 不同图像史料在高中历史教学中的运用策略探析

- 明朝中后期文化发展特性探析

- 还原历史人物的复杂性

- 高中英语教学中学生的主体作用初探

- 浅谈高中英语词汇量的重要性及记忆方法

- appallingly

- appalls

- appalment

- appals

- apparatus

- apparatuses

- apparel

- appareled

- appareling

- apparelled

- apparelling

- apparelment

- apparels

- apparent

- apparentdamage

- apparent/evident

- apparently

- apparentness

- apparentnesses

- apparition

- apparitional

- apparitions

- appeal

- appealabilities

- appealability

- 韭菜命

- 韭菜地——割了一茬起一茬

- 韭菜姑娘

- 韭菜打汤

- 韭菜拌豆腐——一青(清)二白

- 韭菜炒蒜苗——清(青)一色

- 韭菜炖蛋——冒葱(充)

- 韭菜的花

- 韭菜脑袋——割了还能长起来

- 韭菜茎

- 韮

- 韱察

- 韱靡细

- 音

- 音不正

- 音义

- 音义同源说

- 音义隐

- 音乐

- 音乐、歌声等回旋不绝

- 音乐、诗歌

- 音乐上的律吕、宫调等

- 音乐上的维纳斯雕像

- 音乐中交替出现的强弱、长短的现象

- 音乐中每隔一定时间重复出现的有一定强弱分别的一系列拍子