张敏

摘 要:文章主要针对高速并行总线接口信号问题进行研究,首先提出高速并行总线互连设计以及信号完整性相关概念在此基础上提出引起信号不完整的发射、串扰、同步开关噪声以及码间干扰,针对这些问题提出优化策略。

关键词:高度并行总线;接口信号;完整性;优化

1 高速并行总线接口信号完整性概述

1.1高速并行总线互连设计技术

当今信息技术的发展,促进了电气性能的提高与高速发展,电气封装和互连对于信号而言存在“盒子效应”,不再畅通和透明。在这样的背景下人们需要采取新的设计方法来保证电气设计以及电气性能的实现。在高速并行总线互连设计中也需要考虑这一因素,保证设计的科学性、合理性。

首先,在进行高速并行总线设计中应该结合工程建设中积累获得的经验,按照这一设计法则进行高速并行总线设计。其次,在进行高速并行总线互连设计中必须加以量化,对于其性能进行相应预测和评估。

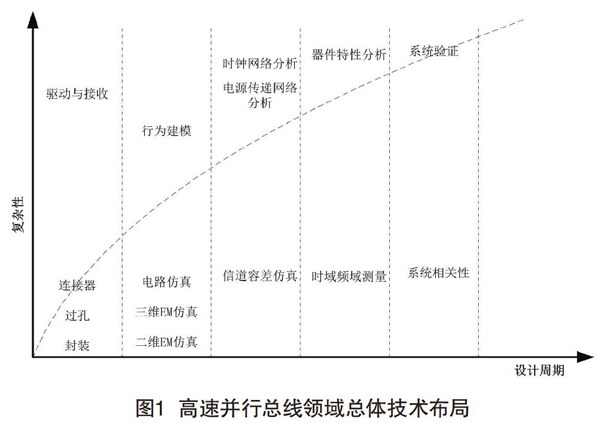

在高速并行总线互连设计中综合利用经验法则、解析近似以及数值仿真、实际测量4种技术[1]。高速并行总线领域总体技术布局如图l所示。

1.2信号完整性概述

信号完整性主要在信号质量上体现,正确的信号时序以及信号电路电压能够保证信号响应。当信号准确时序、信号电压幅值能够准确地传输到IC芯片接收器时,电路就会表现出很好的信号完整性。不能正常将这些信号指标传输到接收器或者传输质量不佳的情况,均属于信号完整性较差。出现信号完整性问题不仅仅是由单一因素引起的,一般是众多因素共同作用的结果。导致信号完整性问题的产生因素包括:元器件布局不合理、芯片开关速度过快、高速信号布线存在问题等,在这些单一因素或综合因素的作用下,系统数据传输不正确,导致整个电路出现问题甚至不能工作。

信号完整性的本质在于保证信源信号能够被接受方正确识别,即使信号传输过程中信道比较复杂。当前电磁环境越来越复杂,传输线效应显著,信号在传输中由于复杂的电磁环境会受到衰减,串扰等因素而出现振铃、过冲等问题,导致接收端信号不能完整接收识别,双方通信难以正常进行。

对于高速并行总线接口信号完整性而言,就是要通过合理手段来规避信号传输过程中存在的问题从而正确地传送到接收端,保证信号参量容限的合理性[2]。

2 反射噪声分析与端接技术

2.1反射噪声原因

信号在传输线中进行传输中,信号幅度主要受到阻抗的影响,阻抗还会受到缓冲器电压、源电阻和传输线的影响。如图2所示,传输线终端会接一个和传输线特征阻抗精确匹配的阻抗。端接到地的信号幅度为V,在传输线上进行传输的过程中电压能够保持V值,这种情况下V值叫作直流稳态值。当传输线终端所接的阻抗和传输线上的特征阻抗不匹配的时候,信号中会存在端接到地的部分,剩余的其他信号部分能够反射回传输线,反射方向沿着朝信号源的方向。反射的衡量指标是反射系数,给定接点出反射电压和入射电压的比值。在电路以及信号传输过程中,反射问题显著。

2.2消除反射的匹配方案

对于数字系统而言,其性能会受到传输线发射的严重负面影响,一般可以通过合理的方法规避或减弱反射导致的不良影响。

(1)降低系统频率。通过对系统的频率进行降低,能够保证信号在传输到传输线之前达到稳态。这种消除反射的方法必须以降低系统工作频率、牺牲系统运行速度为前提,在高性能要求的系统中不适用。

(2)通过印制电路板(Printed Circuit Board,PCB)走线的缩短,实现发射稳态所需时间的减少。这一消除反射的方法的设计中必须增加PCB板层数,这样导致工程建设的成本增加,在实际的生活生产中不常用,而且在理论上也存在局限性。

(3)针对传输线两端的阻抗而言,可以在分别端另外添加一个阻抗,添加的阻抗和传输线特征阻抗相同,通过阻抗的添加来消除发射[3]。

3 串扰噪声及其优化

3.1串扰噪声

串扰主要是针对信号传输过程中电磁耦合而言,一般容性、耦合感性、耦合与辐射、耦合均会引起传输线中产生不期望电压噪声干扰,电流和电压是串扰形成的直接原因。

串扰会对线路信号传输造成危害:(l)串扰会对传输过程中有效特征阻抗和传播速度产生直接的影响,从而影响系统的时序,进而对信号完整性产生不良影响,对于高速并行总线中的传输线性能而言也有所改变。(2)对于其他传输线而言,也会因为串扰引起感应噪声,最终影响信号完整性,主要是对噪声容限的影响。串扰干扰源与被干扰对象分析如图3所示。

3.2串扰优化设计

在高速并行走线互连设计中必须考虑串扰噪声影响,一般可以通过以下手段进行优化设计,尽可能减小串扰。

(l)首先在电路元器件的选型方面,尽可能选择边沿速率较慢的元器件,从而最大限度地减少串扰的影晌。(2)可以通过增大线间距来减小平行走线长度来降低串扰干扰。(3)在进行目标阻抗的设计过程中,应该减小介质层的厚度,这样能够让导体靠近地平面,更好、更紧密地和地平面耦合,最大限度地减小对临近信号线的串扰。(4)采取正确的端接,可以很好地减小反射甚至能够消除反射,这样能够减小串扰[4]。

4 同步开关噪声及其优化

4.1同步开关噪声形成及其危害

同步开关噪声( Simultaneous Switching Noise,SSN)主要是由于多个输出缓冲器发生转换的过程中会产生电流以及电压的突然变化,正是由于这个变化最终导致线路噪声。当电流发生快速变化的时候,电源和地引脚上的电压会发生较大变化,最终引起电源完整性的变化,对电源完整性也会发生变化。

4.2同步开关噪声优化设计

同步开关噪声是高速并行总线运行中必不可少的串扰影响因素,因此必须进行优化设计:(l)采取差分输出驱动器来作为接收器进行信号处理,尤其是对于选通信号以及时钟信号等至关重要的信号而言。(2)对于电容选择而言,可以选用旁路电容等去耦电容来减小同步开关噪声影响。(3)减慢电路中边沿变化率。(4)在电路设计中可以选用比较宽的电源线,对于焊丝尽可能比铰短,这样能够最大限度地减小通路中的电感。

5 码间干扰及其消除

5.1码间干扰概述

在信号进行传输的过程中,复杂的电磁环境以及信号环境必然导致反射、串扰以及其他相关的噪声影响。这些影响会以信号的形式显示在传输线上,对于时序容限以及信号完整性容限造成直接的影响,这些影响统称为码间干扰。

5.2消除码间干扰设计

消除码间干扰可以从以下几个方面入手:(l)针对阻抗不连续问题,进行消除,可以通过源自封装以及插槽等方式增加走线分支长度,而且可以使得寄生效应最小化,最终在高速并行总线上反射也会最小。(2)对于互连通路而言,要使其尽可能短。(3)在电路设计以及规划中,应该尽可能地规避弯曲走线,避免耦合。(4)在选择线长的过程中要合理、科学,在保证信号正常传输的前提下,保证信号完整性网。

6结语

在高速并行总线发展的过程中,时钟频率也越来越高,这样导致互连链路中的各个参数对于线路的信号完整性产生直接影响,对于高速并行总线接口以及相关设计造成极大阻碍。在这样的背景下,必须要采用新的设计方法以及新的设计理念,对于影响信号完整性的反射、码间干扰、串扰以及同步开关噪声等因素进行优化设计,保证信号完整性。

[参考文献]

[1]缑祈科,王妮儿,任崇玉.PCB参数对USB3.0信号完整性的影响[J]兰州理工大学学报,2017 (6):1-5

[2]孔繁,盛卫星,馬晓峰,等.高速背板互连的信号完整性仿真方法[J]系统工程与电子技术,2014 (10):2082-2088

[3]高晓宇,杨龙剑.高速串行通道的信号完整性问题分析[J]通信技术,2013 (6):44-47

[4]张超,余综.基于DDR3系统互联的信号完整性设计[J]计算机工程与设计,2013 (2):616-622

[5]周路,贾宝富.信号上升或下降时间对高速电路信号完整性影响的研究[J]现代电子技术,2011(6):69-73,77

- 旅行的图像:《译文》中的插图与乡土公共性建构

- 南朝石墓门图像组配探究

- 电影策展:实践与经验

- 纪录与收藏

- 收藏、修复与策展

- 池州傩逐疫事象研究

- 福州九案泰山信仰与城市“大傩”

- 蒙古村落傩仪戏剧“呼图克沁”

- 影视剧艺术与文学之间的关联

- 李心峰艺术史研究概观

- 我与艺术史研究

- 贵州当代版画创作与公众审美

- 西南少数民族电影的叙事身份嬗变探究

- 美国综合性大学艺术类专业本科招生模式研究

- 鹰纹中的隐文:早期销美外销瓷“鹰”纹图案探微

- 中、老瑶族婚俗乐舞的风格与形态描述

- 赛博格女孩与福特治理术

- 克拉考尔的“羊皮书”

- “作用于皮肤和头发”:克拉考尔的《电影理论》和1940年的“马赛笔记”

- 论梅党创作的梅兰芳演出剧本的探索

- 梅兰芳的艺术追求与镜鉴意义

- 墓室壁画:封闭空间中的幻像狂欢

- “重生”与不朽

- 重生之路

- 基于贵州布依族枫香印染传统功用的现代创新应用研究

- superindue

- superindulgence

- superindulgences

- superindulgent

- superindulgently

- superindustries

- superindustrious

- superindustriously

- superindustriousness

- superindustriousnesses

- superindustry

- superinfer

- superinfered

- superinference

- superinferences

- superinfering

- superinferred

- superinferring

- superinfers

- superinfinite

- superinfinitely

- superinfiniteness

- superinfinitenesses

- superinfirmities

- superinfirmity

- yáo

- yè

- yé

- yì

- yìn

- yìng

- yìnɡ

- yí

- yín

- yíng

- yínɡ

- yòng

- yònɡ

- yòu

- yóng

- yóu

- yù

- yùn

- yú

- yún

- yā

- yān

- yāng

- yānɡ

- yāo