高敬 张志浩 曹江中

摘要:随着片上系统电源电压的降低,存储器内部电荷泵电路的电压增益不断减小。为提高低电源电压下电荷泵电路的效率,提出了一种新型四相位时钟电荷泵电路,结构采用两路错位时钟驱动电路并将双支路四相位时钟电荷泵电路并联进行输出,消除了阈值电压的损失,有效地提高了电荷泵电路的输出电压,缩短了到达相同电压的时间。最后在TSMC0.18μm工艺下,对电路进行了仿真验证。

关键词:存储器;四相位时钟;电荷泵

中图分类号:TP391? ? ? ? 文献标识码:A

文章编号:1009-3044(2019)28-0263-03

1 引言

电荷泵电路的作用类似于变压器,可以将电源电压一级级抬升,直到达到目标电压为止。电荷泵电路由晶体管和电容组成,是存储器解决片内升压问题的电路。电荷泵电路常用于产生高于电源电压或低于接地电压的直流电压。高压用于执行非易失性存储器的编程和擦除操作[1],低压可用于驱动开关电容电路的模拟模块[2]。衡量电荷泵的关键性能指标之一是输出效率,高效率的电荷泵能为电路提供更高更稳定的电压。

本文提出一种基于传统四相位时钟电荷泵结构的新型电荷泵。该电荷泵的辅助电容不仅仅起辅助作用,而且参与到电压升高的过程,有效地提高了电荷泵电路的输出电压,缩短了到达相同电压的时间,同时采用两路错位时钟驱动电路并将双支路四相位时钟电荷泵电路并联进行输出,减小输出电压纹波。

2 四相位时钟电荷泵

在最早的Dickson电荷泵[3]中,由于使用二极管连接方式作为开关晶体管,在电荷传输过程中,每一次经过开关进行电荷传输时,均存在大小为阈值电压的电压损失,因此输出电压表达式为:

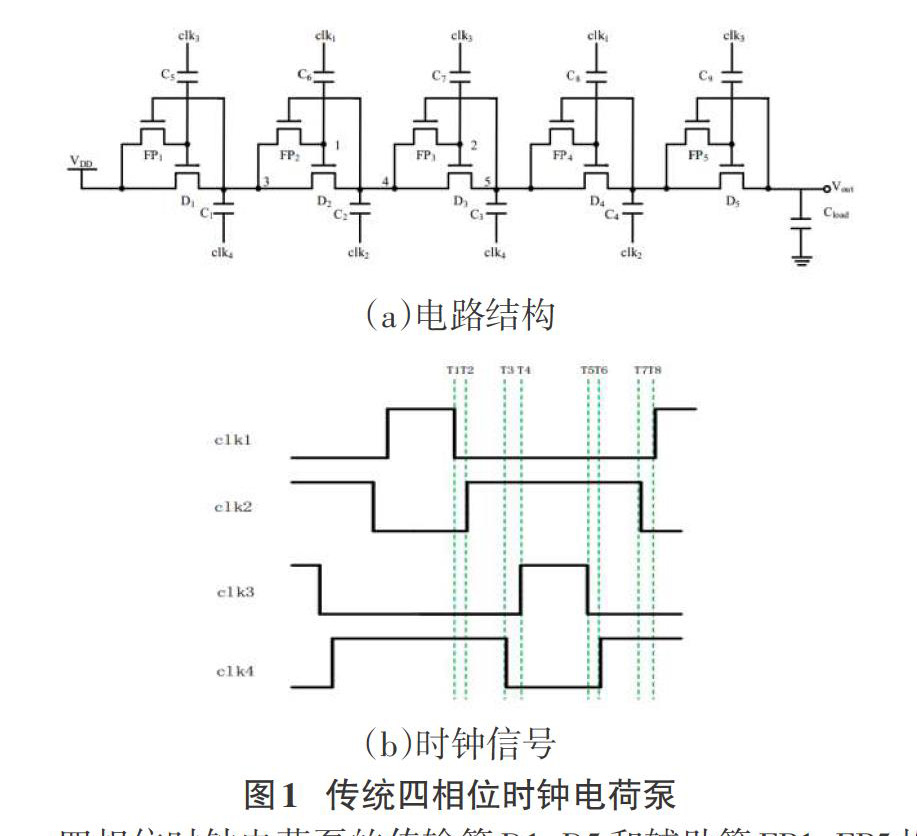

式中[VDD]表示电源电压,N表示电荷泵级数,C表示泵浦电容,[CS]表示节点寄生电容,[Vclk]表示时钟电压幅度,[VTH]表示阈值电压。由上式可以看出,电荷泵电路的输出电压与阈值电压有关,且随着泵级数的不断增多,阈值电压的损失更加严重,限制了电荷泵的最大可输出电压。消除阈值电压影响的一种方法为采用四相位时钟电荷泵结构[4,5],其电路结构和时钟信号如图1所示,其采用非交叠时钟信号控制电路,是为了防止短路和电容漏电,提高电荷泵电路的性能[6]。

(a)电路结构

(b)时钟信号

四相位时钟电荷泵的传输管D1~D5和辅助管FP1~FP5均采用NMOS晶体管,其利用辅助电容C5~C9以及辅助晶体管使传输晶体管在导通时工作在深三极管区,消除了阈值电压损失,以第2级和第3级为例对电路的工作原理进行分析如下。在T1时刻,clk1由高电位变为低电位,clk2和clk3均处于低电位,FP2管截止。在T2时刻,clk2由低电位变为高电位,节点4的电压升高,FP2管导通,同时由于D2管在T1时刻已经截止,所以节点4的电荷不会向节点3进行回流。在T3时刻,clk4由高电位变为低电位,节点5的电压降低,FP3管和D3管均截止。在T4时刻,clk3由低电位变为高电位,clk4为低电位,节点2的电压升高,D3管导通,节点5的低电位与节点4的高电位相同。在T5时刻,clk3由高电位变为低电位,节点2的电压降低,导致D3管截止。在T6时刻,clk4由低电位变为高电位,节点3的电压升高,由于D3管在T5时刻已经截止,节点5的电荷同样不会出现回流现象。在T7时刻,clk2由高电位变为低电位,导致FP2管截止。在T8时刻,clk1由低电位变为高电位,节点1的电压升高,D2管导通,泵浦电容C2和C3发生电荷共享,因此节点4和节点3的电压相同。

电路工作在上述循环过程中,电压从VDD持续升高。相比于Dickson电荷泵,四相位时钟电荷泵的传输晶体管由于在导通时处于深三极管区,消除了阈值电壓损失,因而具有较高的输出电压。

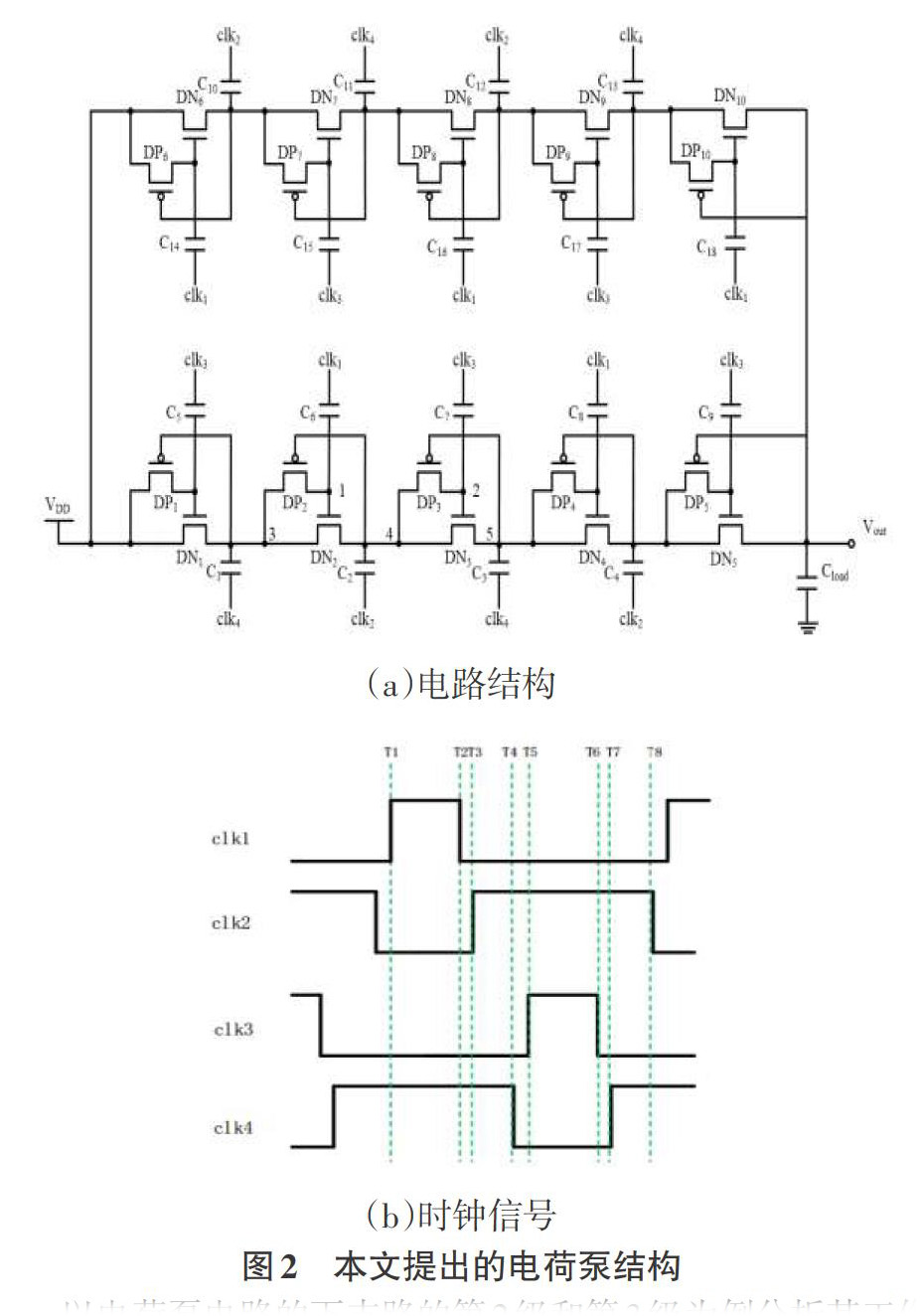

3 新型电荷泵结构

本文提出了一种新型电荷泵结构,电路结构和时钟信号如图2所示。在传统四相位电荷泵电路的基础上,新型结构中辅助管采用PMOS晶体管替代传统四相位电荷泵中的NMOS晶体管,而传输管仍然采用NMOS晶体管。此结构由于辅助电容不仅仅起辅助作用,而是参与到电压升高的过程,因而有效地提高了电荷泵电路的输出电压,缩短了到达相同电压的时间。同时采用两路错位时钟驱动电路并将双支路四相位时钟电荷泵电路并联进行输出,减小了输出电压纹波。

(a)电路结构

(b)时钟信号

以电荷泵电路的下支路的第2级和第3级为例分析其工作原理,将时钟信号分为8个时刻。在T1时刻,clk1由低电位变为高电位,节点1的电压升高,此时DN2管导通,DP2也导通,节点3的电荷向节点4进行传输,因此节点4的电压升高,同时,节点1的电荷向节点3进行传输,节点3的电压会进一步升高,进而将节点4的电压升高的更多。在T2时刻,clk1由高电位变为低电位,DN2管截止。在T3时刻,clk2由低电位变为高电位,节点4的电压经前一过程升高之后再一次进行升高。在T4时刻,clk4由高电位变为低电位时,节点3和节点5的电压降低。在T5时刻,clk3由低电位变为高电位,与T1时刻类似,节点2的电压升高,DN3管导通,DP3管也导通,节点4向节点5进行电荷传输,进而升高节点5的电压,同时,节点2的电荷向节点4进行传输,进一步升高节点4的电压,进而将节点5的电压升高的更多。在T6时刻,clk3由高电位变为低电位,节点2的电压降低,此时DN3管截止。在T7时刻,clk4由低电位变为高电位,节点5的电压经前一过程升高之后再一次升高。在T8时刻,clk2由高电位变为低电位,节点4的电压降低,准备接受节点3进行电荷传输以升高电压。

4仿真结果

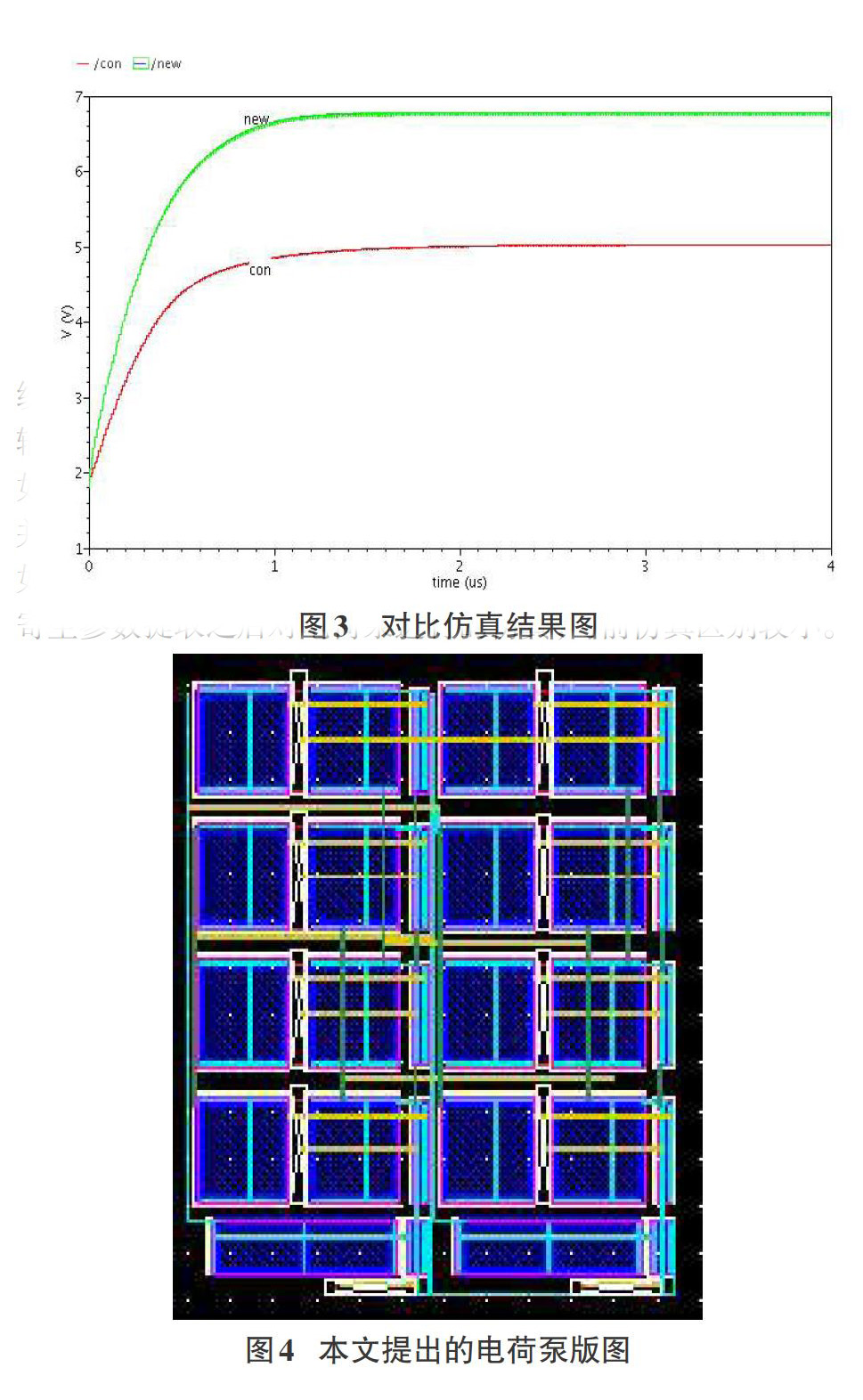

在TSMC 0.18μm工艺下,只有电容负载的情况,电源电压和时钟电压幅度均为1.8V,对本文提出的新型电荷泵和传统电荷泵进行对比仿真,仿真结果如图3所示。进行对比仿真时,两种电荷泵电路的仿真条件相同,并均采用双支路并联电路结构,其中new表示本文提出的新型四相位时钟电荷泵,con表示传统四相位时钟电荷泵。

由图3中可以看出,在仿真条件相同的条件下,相较于传统四相位时钟电荷泵,本文设计的新型电荷泵电路具有较高的输出电压,到达相同电压的时间更短。新型电荷泵设计的版图如图4所示,由占大部分面积的电容和一些高压MOS管组成,并对其进行DRC、LVS验证和寄生参数提取之后的后仿真结果如图5所示,仿真条件与前仿真相同。由图5中可以看出,经过寄生参数提取之后对电荷泵进行的仿真,与前仿真区别较小。

5结束语

本文提出了一种基于传统四相位时钟电荷泵的新型电荷泵结构,通过辅助电容参与到电压升高的过程,同时采用两路错位时钟驱动电路并将双支路四相位时钟电荷泵电路并联进行输出,减小输出电压纹波。采用TSMC 0.18μm工艺对电路进行了仿真验证,结果表明电荷泵有效地提高了电荷泵电路的输出电压,并完成了电荷泵的版图设计和后仿真。

参考文献:

[1] Kawahara T , Kobayashi T , Jyouno Y , et al. Bit-line clamped sensing multiplex and accurate high voltage generator for quarter-micron flash memories[J]. IEEE Journal of Solid-State Circuits, 1996, 31(11):1590-1600.

[2] Wu J T , Chang Y H , Chang K L . 1.2V CMOS switched-capacitor circuits[C]// 1996 IEEE International Solid-State Circuits Conference. IEEE, 1996.

[3]Dickson, J. F . On-chip high-voltage generation in MNOS integrated circuits using an improved voltage multiplier technique[J]. IEEE Journal of Solid-State Circuits, 1976, 11(3):374-378.

[4] KuriyamaM ,Atsumi S , Umezawa A , et al. A 5 V-only 0.6 μm flash EEPROM with row decoder scheme in triple-well structure[C]// IEEE International Solid-state Circuits Conference. IEEE, 1992.

[5] SteenwijkV ,Hoen, Wallinga. Analysis and Design of a Charge Pump Circuit for High Output Current Applications[C]// European Solid-state Circuits Conference. IEEE, 1993.

[6] 万悦, 吕坚, 周云, 等. 一种具有对称结构的低损耗低纹波电荷泵[J]. 微处理机, 2018, 189(3):3-7.

【通聯编辑:唐一东】

- 高职C#程序开发改革研究

- 开放教育实践环节教学工作中存在问题及对策探索

- 物联网工程专业实践课程建设

- 试论信息技术支持下高职技能型人才校企合作培养模式

- 基于移动网络的动画设计课程移动微课学习资源的设计与开发

- 浅谈培养学习计算机兴趣的方法

- 大数据技术实验室建设探索与研究

- 新形势下信息技术基础课程的教学改革研究

- C编程教学导入线索分析

- 网络工程专业应用型人才培养模式改革探索

- 基于APP inventor编程工具的移动学习支持平台的开发与应用

- 高职“双循环”模式的课程开发研究与实践

- 互联网+思维下提升高职“双创”人才信息素养的意义与对策

- 高职软件技术专业现代学徒制人才培养模式探究

- 云打印模式在高校市场中的优劣势比较

- 中等职业学校《计算机应用基础》课程能力培养及教学对策

- 在高职院校一种基于微信的泛在学习研究

- 小议中职学校计算机专业建设的几点看法

- 高中信息技术课程教学中PBL教学模式的应用探索

- 基于网络平台《计算机应用基础》数字化系统的研究与设计

- 基于微信平台的教育创新路径的研究

- “豪恩斯坦的知识分类方法”微型学习过程的设计

- 翻转课堂教学模式在高职计算机基础课程教学中的应用

- 医学高校计算机公共课的移动学习平台研究

- 基于Matlab GUI的直杆斜抛运动仿真

- excitingest

- excitingly

- excitingness

- excl

- excl.

- exclaim

- exclaimed

- exclaimer

- exclaimers

- exclaiming

- exclaims

- exclamation

- exclamational

- exclamation mark

- exclamation point

- exclamations

- excludability

- exclude

- excluded

- excluder

- excluders

- excludes

- excluding

- exclusion

- exclusioner

- 楸

- 楸函

- 楸局

- 楸枰

- 楸棋

- 楸榆

- 楸玉局

- 楹

- 楹书

- 楹帖

- 楹柱

- 楹栋

- 楹联

- 楹西

- 楹语

- 楻板

- 楼

- 楼丁

- 楼上

- 楼上元龙

- 楼上摆花盆——无地自容

- 楼上楼

- 楼上的小户

- 楼下

- 楼下客满——后来居上