周婷婷

【摘要】 根据ARINC429航空总线工业标准,按照ARINC429总线的电气特性要求,采用FPGA+DSP的架构实现多种ARINC429协议处理。FPGA结合外围芯片实现ARINC429总线底层数据收发功能,DSP实现ARINC429总线AIM、BOP3协议解析功能。该实现具有设计简单灵活,应用场景广,具备一定抗干扰能力等特点。该设计已应用于采用ARINC429总线的航空通信设备。

【关键词】 ARINC429 FPGA DSP AIM BOP3

Design and Implementation of Multiple protocol processing for ARINC429 Bus in the aviation communication equipment

ZHOU Ting-ting(Southwest China Institute of Electronic Technology,Chengdu 610036,China)

Abstract: According to the ARINC429 aviation bus industry standards, in accordance with the requirements for the ARINC429 bus electrical characteristics, FPGA+DSP architecture was adopted to realize a variety of protocol processing. FPGA combined with peripheral chips to realize the function of underlying data transceiver for ARINC429 bus, DSP to realize the function of AIM and BOP3 protocol parsing for ARINC429 bus. This implementation is simple in design, flexible application scenario is wide, have a certain anti-interference ability, etc. This design has been applied in the aviation ARINC429 bus communication equipment.

Key words: ARINC429;FPGA;DSP;AIM;BOP3;

一、引言

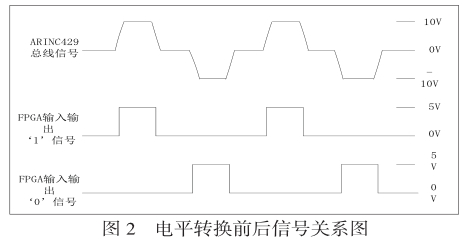

ARINC429是一种通用航空电子总线标准,它是由美国航空电子工程委员会(Airlines Engineering Committee)1977年提出,并于同年颁布实施 ,广泛应用在军用和民用航空电子领域。ARINC429总线采用双极性归零码调制,数据字(32bit)以脉冲形式发送,发送脉冲有三个电平,即高电平(+10V)、0电平(0V)、低电平(-10V)。字与字之间间隔(至少4bit)分开。有两种可选速度:高传输率100kbps(±1%)和低传输率12.5Kbps(12.5kpbs到14.5kbps)。根据ARINC429总线的电气特性,需要外围电路实现总线與FPGA之间的电平转换。本设计选用HOLT公司的芯片HI-8586、HI-8588-10完成电平转换。

二、方案设计

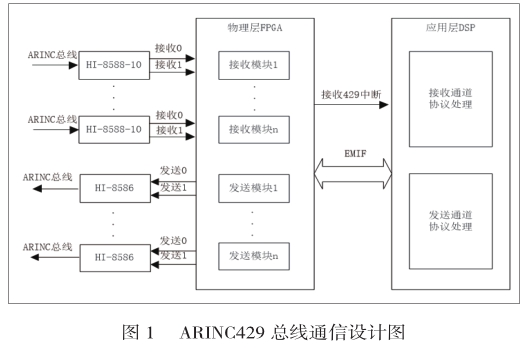

为了实现多通道数据收发,多种传输协议通信,本设计采用分层式设计结构,设计简单灵活,具备良好的可移植性、重用性和扩展性,应用场景广,具备一定抗干扰能力。物 理底层采用FPGA实现ARINC429总线数据收发功能,应用层采用DSP实现ARINC429总线传输控制字AIM和数据传输协议BOP3等的解析应用,共同完成ARINC429总线控制和数传通信要求。ARINC429总线通信方案设计如图 1所示。

三、FPGA设计

3.1 FPGA输入输出时序

FPG A接收和发送的ARINC429信号,要经过芯片HI-8588-10和HI-8586进行电平转换,转换前后的信号格式如图 2所示:

3.2 FPGA接收模块设计

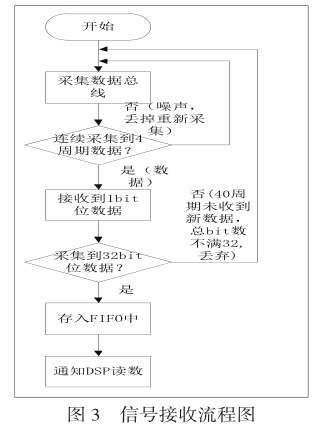

FPGA收到转换后的信号,采用10倍高钟采样数据,考虑到TTL电平是半 周期宽度,即如果ARINC429总线速率是100 KBPS,则脉冲宽度是5μsec,再除去上升沿、下降沿的误差,则累计连续采集4周期以上为信号数据,其它为噪声,由此可以去除接收信号上的干扰毛刺。

因此,专门设计一个采集数据计数器,采集到‘1,开始计数;采集到‘0,计数器清零。可以通过对计数器大小的判断来确定是否为 接收信号。另外设计一个数据位数计数器对接收位数进行计数,当接收完一个429字后,生成FIFO的使能信号,将数据存入FIFO中。如果收到bit位数据后连续40周期未收到新数据,且bit位总数不满32,丢弃该数据。接着生成DSP中断信号或查询标志 ,通知DSP读取数据。接收数据流程如图 3所示。

3.3 FPGA发送模块设计

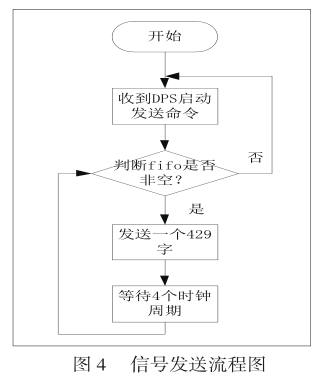

发送时,FPGA采用异步FIFO对DSP发送数据进行缓存,发送时钟 按照ARINC429总线速率要求分频产生。

FPGA接收到DSP启动发送命令,检测FIFO空标志,如果FIFO非空,则读取一个429字发送,发送完成后再读下一个429字发送,直到FIFO发空为止。发送过程中,两个429字之间,要空闲4周期以上,40周期以下。发送数据流程如图 4所示。

四、DSP设计

4.1 AIM数据

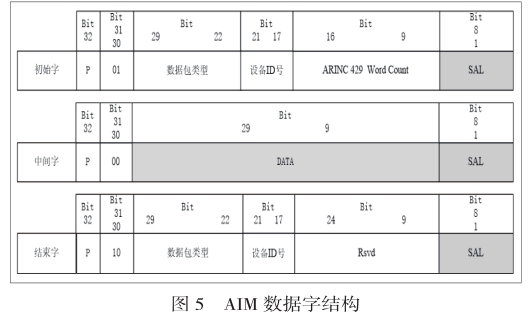

AIM数据是ARINC429数据形式的一种,包含初始字、控制字(任选)、中间字(任选)和结束字等,AIM数 据传输的特点是标号始终不变。本设计使用AIM数据进行控制消息传输,选取初始字、中间字和结束字三种数据字,其数据字结构如图 5所示:

在本设计中,DSP收到AIM数据,对数据字进行奇偶校验和标号判断,通过后的数据再进行协议解析。首先判断字类型,收到初始字,提取数据长度、设备ID号和包类型等信息;收到中间字,提取数据信息;收到结束字,提取包类型和设备ID号等信息,并与初始字提取信息相比较,如果都相符则一帧接收完成。数据解析流程如图 6所示:

4.2 BOP3数据

BOP3是ARINC429的一种文件传输协议,本设计选取BOP3进行数据传输通信。BOP3传输的数据内容可以达到1023个字,该协议为MAC层协议,包含了“429 MAC控制子层”和“429 介质访问控制”两个层次。其协议架构如图7所示:

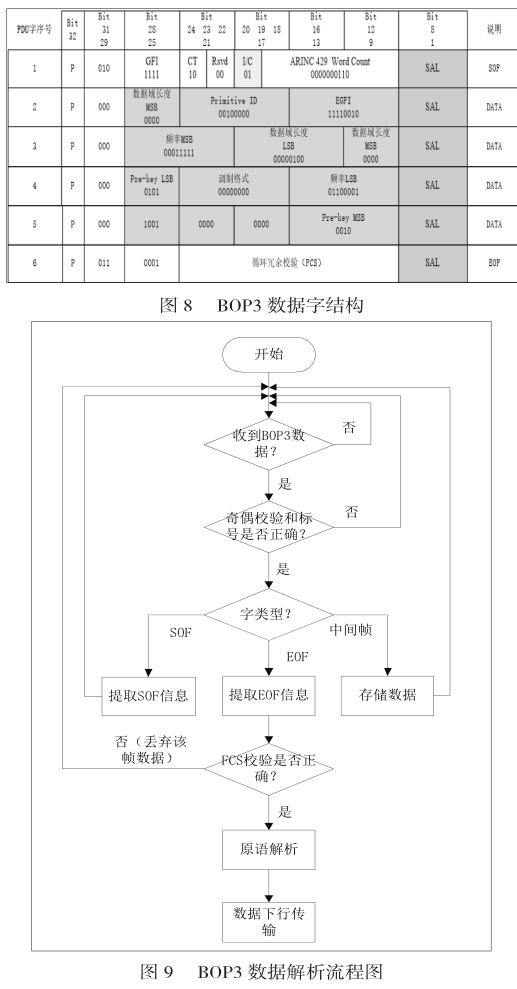

“429介质访问控制”层次负责封装信息和提取信息,该层次协议由一个控制帧SOF、若干个数据帧和一个控制帧EOF组成一条完整的命令类消息。其数据字结构如图 8所示。

“429 MAC控制子层”负责流量控制和数据传输,该层次协议提供了四个原语作为MAC层与链路层的接口,四個原语中,其中MA_CONTROL负责MAC层的流量控制,为选用;MA_DATA为需要物理介质传输的内容。

在本设计中,DSP收到BOP3数据,对数据字进行奇偶校验和标号判断,通过后的数据首先进行第一层协议解析,收到SOF提取信息,收到数据帧存储数据,收到EOF后进行FCS校验。解析出原语后,再进行第二层协议解析,根据协议内容进行上下行数据传输。数据解析流程如图 9所示:

五、结束语

本文实现了ARINC429总线控制和数传通信要求,除使用少量外围芯片,主要功能都由FPGA和DSP来实现,整体架构灵活可变,可以根据项目具体要求进行局部调整,以适应不同需求。该设计稳定、可靠,具备良好的可移植性、重用性和扩展性,具有较高的实用价值。

参 考 文 献

[1]蒋学东,刘勇。 用FPGA实现ARINC429接口和总线数据接收。现代电子技术,2010年06期。

[2]刘连生,姜健飞。基于FPGA的ARINC429多通道芯片设计。微电子学,2010年01期。

[3] ARINC Specification 429P3-19,Mark 33 Digital Information Transfer System(DITS)-Part3-File Data Transfer Techniques.

- 公体正用,体用一如

- 东南亚香药与明代饮食风尚

- 卡罗·金兹堡微观史学研究的理论指向

- 韩国历史编纂学中的民族主义

- 一部奇异家书

- “奉旨归堂”:康熙宫廷西洋教士寻求皇帝宽容天主教的活动(1669—1671)

- 《两广盐利疏》考

- 官、民与法

- 唐宋时代的科举与党争

- 东汉丧礼送葬考

- 柏拉图《法律篇》刑法条文选译

- 《尤利乌斯—母神殖民城法令》译注

- 古巴比伦王朝西帕尔城奴隶买卖契约研究

- 夒膚瑚铭文新释

- 《雅典胞族法令》译注

- 伊索克拉底《泛希腊集会演说辞》中“领导权问题”矛盾论述出现的原因

- 宁乌尔塔神话

- 罗马帝国情报系统的建设

- 亚述帝国宦官的地位与作用

- 中世纪英格兰劳工法令的颁布、执行及其影响

- 管窥《王室法兰克年代记》的官方属性

- 罗马帝国衰落的起点

- 罗马国家统治制度的创新

- 印度史家苏米特·萨卡尔的社会史观及其对“底层研究”转向的批评

- 民族主义、现代性、东方主义、后殖民主义

- breakage

- breakages

- break a promise

- break a rule/law

- break-away

- break away

- breakaway

- break away from

- break away (from sb/sth)

- breakaways

- break-back

- break-camp

- breakclause

- break clause

- break-dancing

- break down

- break-down

- breakdown

- breakdowns

- breakdown truck

- breaker

- breaker-points

- breakers

- break even

- break-even

- 过咎

- 过哈哈儿

- 过哪河,脱哪鞋

- 过嘴截舌

- 过嘴舌

- 过嘴说

- 过场

- 过场戏

- 过城门刮耳朵——大头

- 过埠新娘

- 过堂

- 过塑

- 过境贸易

- 过多

- 过多的考虑

- 过多的赏赐

- 过多贪求而受不了

- 过夜

- 过大堂

- 过天

- 过太平日子

- 过失

- 过失与悔恨

- 过失和邪恶

- 过失或错误