吉茂林 王玮

摘要:本文主要介绍了航空电子产品的信号完整性设计中信号传输损耗控制、信号反射处理、信号串扰控制、差分互联设计,并根据设计分析,对产品出现的问题进行了改进。

关键词:信号完整性;信号反射处理

一、引言

航空电子产品设计过程中时常会遇到一个问题:在设计高频高速信号电路时,未考虑信号完整性问题带来的影响,导致信号质量差,装机后在复杂工作环境中不满足产品性能要求。

为了解决上述电子产品设计过程中存在的可靠性问题,开展信号完整性设计分析。目的是在PCB设计中就考虑影响信号完整性的因素,设计过程中或设计完成后利用仿真进行定性或定量分析,进而排查并优化可能存在的风险问题,以提高电路健壮性。

二、信号完整性概述

信号完整性是指信号传输过程中能够保持信号时域和频域特性的能力,即信号在电路中能以正确的时序、幅值以及相位等做出响应。信号完整性主要包括以下几个方面內容:

(1) 信号沿印制板传输线传递时,由于辐射损耗、导线损耗和介质损耗,会使信号强度衰减。必要时,需对印制板传输线的衰减常数进行测定或计算。(2) 信号传输过程中,只要遇到瞬时阻抗突变,就会存在反射和失真,现象包括:振铃、边沿是否单调、过冲/下冲、边沿台阶。(3) 串扰是两条信号线之间距离相近产生耦合,在信号线之间的互感和互容而引起的噪声,在高频、高速电路设计时,应重视信号串扰。(4) 差分互连是利用存在耦合的传输线进行信号输入输出,抵御差分串扰的鲁棒性高,且具有对抗返回路径间隙阻抗突变的能力。

三、信号反射处理设计分析

(一) 信号反射处理注意事项

(1) 用可控阻抗走线;(2) 端接电阻应靠近封装焊盘;(3) 每个信号应有返回路径,且位于信号路径下方,宽度不少于信号路径的3倍;(4) 同一个网络同层的信号走线不宜改变线宽;(5) 同一个网络的信号走线应减少换层、打过孔;(6) 点对点拓扑时,可采用驱动端串联端接或接收端并联端接;点对多点拓扑时,可选用末端并联端接;(7) Fly-by 结构通常比菊花链结构信号质量好,走线时桩线长度应尽量短;(8) 不宜存在跨分割;(9) 回波损耗应满足设计要求;

(二)设计问题及改进

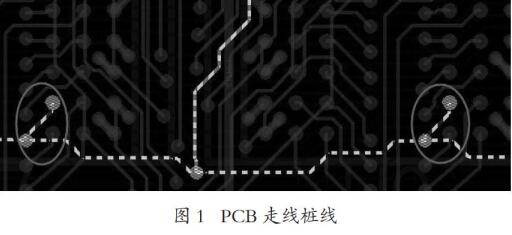

某产品的DDR3电路模块用一个处理器 驱动4 片DDR3。由于信号是800MHz,采用了Fly-by结构,桩线相较于菊花链结构要短。而桩线越短信号的反射越小,走线桩线如图1所示。该电路采用末端并联端接方式,使用DDR3的ODT功能,端接电阻器集成在DDR3 芯片内部。

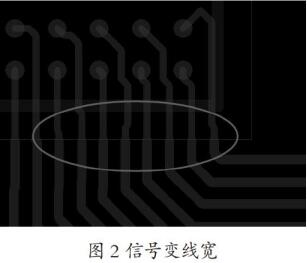

初始设计时,因BGA底部的布线空间有限,在BGA 底部用的4.5mil线宽,出了BGA底部后用的6mil线宽,如图2所示,这部分线宽变化导致了阻抗变化,造成了信号反射。

设计改进后,整个网络信号走线宽度保持4.5mil不变,阻抗不变。

此板设计为6层板,有3个布线层,DDR3部分的控制和地址线打2个过孔即可,如采用4层板,则需要多打过孔,而过孔是阻抗不连续点,会出现信号反射。因此此处采用6 层板方案,尽量减少了打过孔的数量。

如图3所示,3个走线层均有完整的参考层,不存在走线跨分割的情况。GND1和GND2均为完整的地平面,TOP参考GND1层,SIG1和BOTTOM参考GND2层。

四、结束语

传统的电路设计方法是根据要求研制产品样机,然后进行电路调试,调试过程中通过测试发现问题,然后重新设计再次加工调试,即所谓“试错”方式。这种方法开发周期长,成本很高,有时出现的问题可能需要多次改版才能解决。如今产品的研制时间和产品的成本、性能同等重要,采用传统做法效率会很低。如果在设计初期不考虑信号完整性,就很难做到一次成功。

参考文献:

[1]《信号完整性分析 Signal Integrity:Simplified》 [美] Eric Bogatin 著,李玉山、李丽平 等译,电子工业出版社

- 小学数学分数应用教学的三个技巧

- 游戏在小学低年级数学课堂教学中的作用

- 如何在小学语文识字教学中进行文化熏陶

- 浅谈小学低年级语文教学中如何培养学生的自主学习能力

- 初中思想品德教育体系的构建

- 浅谈对农村体育教师继续教育的认识

- 如何培养学生积极的情感态度

- 小学德育工作的有效性探析

- 浅谈初中语文教学中的德育渗透

- 独立精神教育之魂

- 折出一片异彩纷呈

- 在语文教学中提高学生的阅读能力

- “多元解读”,切实提高学生阅读能力

- 小学生自主学习能力培养策略

- 初中语文阅读教学的实施策略

- 小组合作探究实效性提升策略

- 初中语文综合实践活动课多样化研究

- 建构思想品德生态课堂教学模式的研究

- 农村初中英语学困生的转化

- 语文课堂有效教学的思考

- 展示思维过程 激发学生创造力

- 创新课堂教学 提高学习效率

- 浅谈初中体育课中游戏教学的运用

- 初中语文课堂有效提问策略

- 高效课堂下小学班主任工作的几点反思

- internationalities

- internationality

- internationallabourorganization

- international labour organiˌzation

- internationallabourstandards

- internationallaw

- international law

- internationally

- international management

- internationalmanagement

- internationalmonetarysystem

- internationalmotorinsurancecertificate

- international motor inˌsurance cerˌtificate

- international reply coupon

- internationalreplycoupon

- internationalreserves

- international reserves

- internationals

- bigger

- biggest

- bigging

- biggish

- big-head

- big-headed

- bigheaded

- 哀愕

- 哀感天地

- 哀感顽艳

- 哀慽

- 哀戚

- 哀挽

- 哀挽文人不寿辞

- 哀摧

- 哀敬

- 哀文悼词

- 哀时命

- 哀梨

- 哀梨并剪哀梨脆枣

- 哀梨蒸食

- 哀梨蒸食——可惜了好东西

- 哀楚

- 哀欢离合

- 哀歌

- 哀死事生

- 哀死问伤

- 哀毁

- 哀毁瘠立

- 哀毁致病

- 哀毁骨立

- 哀求