孙靖舒

摘要:随着科学技术的不断发展,如今社会对于电子设备的结构与功能要求也在日益提升。为此,该文将设计出一种体积小、能耗低的通用数字信号处理系统,并在系统中采用FPGA为系统的硬件加工,以DSP为数字处理核心,最终对其他硬件没备进行有效控制。

关键词:DSP;FPDA;通用数字信号处理;系统设计

中图分类号:TP311

文献标识码:A

文章编号:1009-3044(2020)20-0221-02

随着信息技术和电子技术的不断发展,如今数字信号处理已经被广泛地运用到各行各业中,并发挥出良好的应用效果。但随着人们对于电子设备功能需求的日益增加,如今电子没备的结构也越来越复杂,其不仅极大地增加电子设备的体积和运行能耗,还有可能影响到没备的实际运行效果。为此,本文将没计出一种能耗低,体积小的通用数字信号处理系统,以期能够为业内人士提供理论参考。

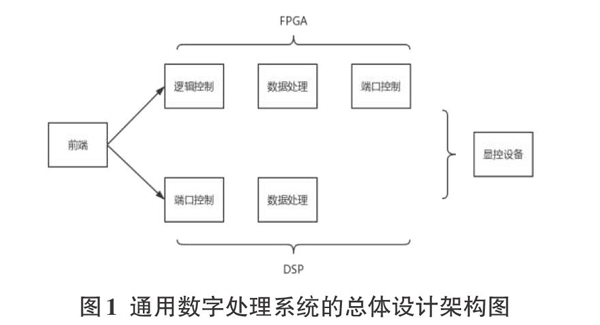

1系统总体设计

本文所没计的基于DSP和FPGA的通用数字信号处理系统,其实际总体没计架构如图1所示。整个系统有前端、FPGA、DSP以及显控设备四部分共同组成,其中前端设备在系统中用于数字模拟信号的输工作;FPGA则是用于控制ADC和DAC部分,其中ADC主要是对前端所输出的信号进行数据采集、滤波、变频、抽取、处理以及对系统外部端口电路进行实时逻辑控制,而DAC则是负责与DSP接口相互连接,然后通过输出基带信号来对DSP部分进行逻辑控制;DSP部分是本系统设计中数字核心处理部分,该部分是本系统没计中的核心部分主要负责通过核心算法对FPGA所传递出的模拟信号进行进一步的分析和处理,并在处理完成后,得到的数据传递给显控没备进行实际显示。

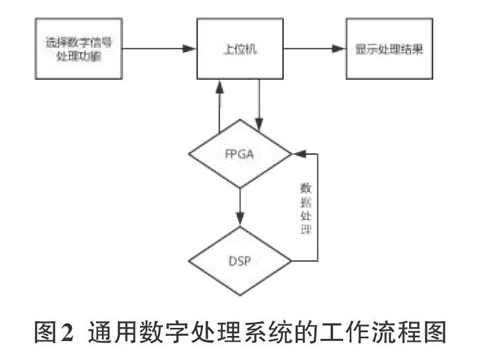

在实际运行过程中,本文所没计的通用数字处理系统的工作流程如图2所示。操作者可以通过上位机的人机交互界面来选择实际数字信号处理功能,并通过USB接口来将上位机的控制命令传递给FPGA,之后FPGA又会将命令指令传递给DSP,DSP将会根据上位机所发布的指令来对数据进行实际处理,并在完成处理后,将经过处理的数据传回给FPGA,最终FP-GA则又会通过USB接口将处理后的数据传递给上位机,再由上位机的显示程序和人机交互界面进行显示[1]。

2系统的硬件设计

本文所设计的数字信号处理系统硬件部分主要包括有DSP和FPFGA两大部分,以下为该两部分的具体硬件没计内容。

2.1DSP部分硬件设计

DSP部分作为本文所没计的数字信号处理系统的核心组成部分,其有着运算速度快、数据处理能力强等特点,并且在实际使用过程中,使用者还可以结合自身的实际所需,在DSP部分上拓展若干个存储器件。

作为本设计的核心部分,本系统设计大部分数字信号处理功能都需要通过DSP硬件部分来完成,所以DSP硬件部分选择将会直接关系到本系统没计的实际应用效果。在对系统的实际运算需求、DSP硬件没备价格、通用化程度以及其他多方面进行综合考虑以后,最选择了T1公司的C55x系列的TMS320C6455高性能定点数字信号处理器。该定点数字信息处理器,主频达到了1GHz,1ns的指令周期。每周期执行8条32位指令,最大峰值速度达到8000MIPS。TMS320C6455还带有Seria/RapidlOfr)总线,互连速率每秒高达25(Gbits,实现了极高的多处理性能,降低了系统能耗,比传统的外部存储器接口快12倍,这使得多DSP级连变得十分方便。

其次,该定点数字信息处理器片内是基于C64xx内核的L1/L2存储结构。片上集成有大量的存储空间,LIP为32K字节,LID为32K字节L2为2M字节,LIP和L2都可直接映射到存储空间。

最后,该定点数字信息处理器还设置有McBSP接口、IC接口、DDR2接口、PCI接口、64位EMIF接口以及10/100/1000M以太网媒体访问控制器。因此,其完全可以满足本通用数据信息处理系统设计中对于DSP的实际功能需求。以该定点数字信息处理器为基础,本系统所设计的DSP硬件部分可以实现以下几方面功能。

(1)拓展SDRAM用于存储需要处理的数字信号,拓展Flash用于初始化数字信号处理程序以及FPGA的配置文件。

(2)在DSP部分完成復位初始化以后,DSP硬件部分还可以结合FPGA部分实现应用程序的即时运行,进而完成数字信号的运算处理工作。

(3)DSP硬件部分与FPGA之间的即时通信使得系统各模块、各程序之间的调度达到了协调统一的效果。

2.2 FPGA硬件部分设计

对于FPCA硬件部分,为能够保障该部分能够实现高度并行体系结构、高数据率以及数据处理时间可控等方面要求,本系统在设计时候最终选择了Xilinx公司的XC5VSX95T-IFF1136C作为中央处理器,从而对本系统中的数字信号处理功能进行有效控制。

在使用该中央处理器以后,本系统中的FPGA硬件部分将可以实现以下几种功能:

(1)通过系统中所拥有的EMIFA总线,对DSP硬件部分进行控制,从而DSP硬件部分可以实现与FPGA硬件部分的即时数据交互活动;

(2)系统运行过程中对于数字信号的编解码、通道控制、数字信号和通道的实时控制都可以通过FPCA部分来完成;

(3)在系统上电时,无论是FPCA硬件部分、DSP硬件部分,还是Flash加载程序,都需要有CPLD来进行实时监控。系统会先行加载FPGA硬件部分,再通过FPGA硬件部分的数据传输来加载DSP硬件部分,从而完成系统的上电启动工作;

(4)在系统运行过程中,FPCA硬件部分需要通过I/O线路来实现与其他硬件部分的数据与数字信号交互活动,其中数字化中频率数据将会由输入通路接受,而激励模块所发送的待调制的亟待数据则会有输出通路进行传输[2];

(5)在本系统中FPGA硬件部分的莪术油外部接口是I/O通用接通,其需要FPGA硬件部分通过自身的I/O接口通过加隔离驱动的方式完成线路连接驱动活动。

3系统的软件设计

3.1DSP程序设计

在进行通用数字信号处理系统中软件部分没计的时候,考虑到系统的通用性以及DSP硬件部分的实际兼容性,最终选择了Tl公司专门为DSP准备的程序没计开发环境——CCStudiov3.3来作为本系统软件设计的实际开发环境,最终选择C语言为开发语言,根据图3中的DSP程序工作流程,完成通用数字信号处理系统的软件系统没计工作[3]。

如图3所示,在DSP程序运行过程中,DSP程序首先为对内部寄存器资源精细化合理配置,然后对EMIF和CPU频率进行初始化;其次DSP程序会结合DSP硬件部分的实际功能,对FP-GA所传递命令字进行解读,然后根据解读结果选择自动选择相应的功能,并读取FPGA所传递的数字信号,通过DSP的相关子程序进行相应的处理和分析技术,再将处理结果回馈给FP-GA,最后FPGA会将已经完成处理的数据写入到FIFO中,并通过USB接口上传到上位机,由上位机进行显示和判断,若是数字信号处理正确,那么上位机便会将处理后的数据直接输出,但若是处理错误,那么上位机会重新发出命令字,重复上述的工作流程,直到输出数据正确为止[4]。

3.2上位机应用程序设计

正如上文所述,本文所没计的通用数字信号处理系统中,上位机的主要功能为命令功能选择、输m数据正确性判断以及数据输出三大方面。为能够最大限度地保障本系统中上位机的通用效果,选择了NI公司的LabWindows、CVI集成软件开发环境来进行上位机应用程序设计。结合上位机的实际功用效果,最终所设计的上位机应用程序不仅可以通过人机交互界面进行命令字功能选择,还可以通过上位机编码,借助USB接口来将输出结果存储到计算机中,并在计算机进行显示,同时在此过程中完成数据的正确性判断,若不正确则会反馈在人机交互界面,方便操作人员进行参考和功能修改。

4结语

本文提出了一种基于DSP和FPGA的通用数字信号处理系统没计,该系统部件有着体积小、功耗和成本低的特点,还能够适应当今对于数字信号处理的实时性和高速性要求,可以满足大部分数字信号的处理,因而有着较强的应用型价值。

参考文献:

[1]郑伟亮,张贝贝.基于DSP+FPGA的数字信号处理系统没计[J].深圳信息职业技术学院学报,2007(4):56-59.

[2]刘魁,刘健,管增伦,等.基于DSP+FPGA+CPLD的電力电子设备通用控制器[J].电子技术应用,2019,45(04):129-133+141.

[3]李伟.基于DSP和FPGA的高速数字信号处理系统设计[J].中国新通信,2015,17(11):127-128.

【通联编辑:代影】

- 现代物理学渗透于高中物理教学的研究分析

- 浅谈兴趣教学在初中英语教学中的应用

- 高中数学教学中学生主体参与意识的培养

- 语文教育与人文主义教育的完美融合

- 新课改下初中语文作文教学改革探索

- 阅读促进下的英语作文写作策略研究

- 谈谈化学教学中学生迁移能力的培养

- 浅谈人本主义在高中政治教学中的运用

- 运用认知灵活理论指导高中化学概念教学

- 探究初中英语写作支架式教学体系的构建

- 培养高一学生数学学习习惯的几点策略

- 高中英语阅读的策略与技巧研究

- 初中政治教学有效性分析

- 让化学教学回归生活世界

- 美就在身边

- “学案导学,自主探究”教学模式探微

- 如何培养初中生的化学阅读能力

- 以人为本,有效开展感悟式语文教学

- 在历史教学中促进职校生人格优化

- 初中生物教学实验研究

- 探究初中化学实验教学的有效性

- 信息技术在高中英语课堂教学中的应用研究

- 汉译英中的常见问题分析

- 中职语文教学中应用文写作生活化的实践教学研究

- 优化中学信息技术教学策略探究

- immensenesses

- immenser

- immensest

- immensities

- immensity

- immerse

- immersed

- immerser

- immerses

- immerse yourself in

- immersing

- immersion

- immersionist

- immersions

- immigrant

- immigrants

- immigrate

- immigrated

- immigrates

- immigrating

- immigration

- immigrational

- immigrations

- immigrators

- immigratory

- 伯尔

- 伯尔尼

- 伯希和

- 伯庸

- 伯强

- 伯恩斯坦

- 伯恩施坦

- 伯成子高

- 伯昌

- 伯明翰

- 伯有

- 伯林

- 伯格长

- 伯桃

- 伯樂

- 伯歌季舞

- 伯母

- 伯母、叔母

- 伯氏

- 伯氏无儿

- 伯爵

- 伯父

- 伯父的妻子

- 伯父,叔父

- 伯爷