武坚 武健 张宇烜

摘要:基于FPGA的嵌入式结构产品在硬件设计领域得到了广泛应用,该文介绍了Virtex系列FPGA的逻辑加载模式,对加载速度较高的Slave SelectMAP模式的逻辑加载过程进行了研究,并分析了加载中各信号的使用情况。同时结合产品使用实例,对典型的逻辑加载故障进行了分析和研究。

关键词: Slave SelectMAP模式 ;逻辑加载故障

中图分类号:TP3? ? ? ? 文献标识码:A

文章编号:1009-3044(2020)36-0232-02

1 介绍

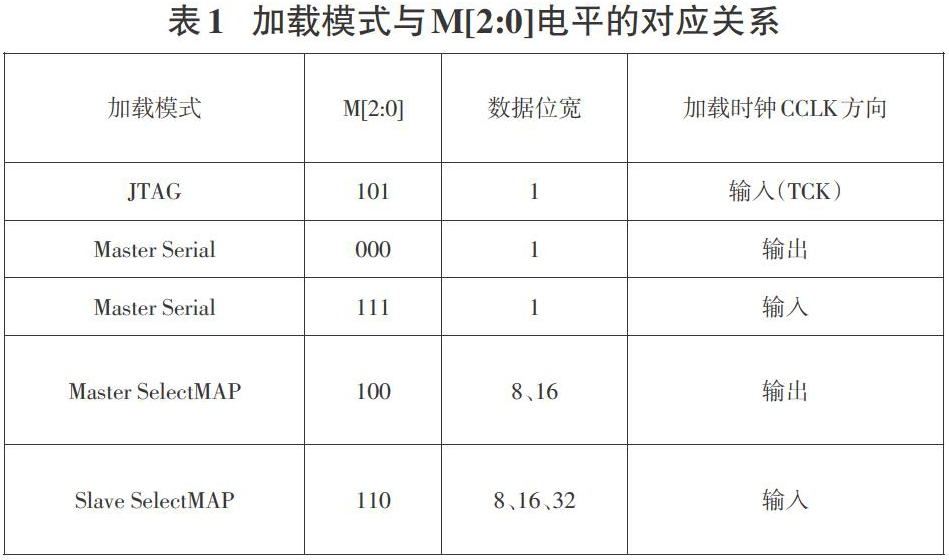

以高密度现场可编程逻辑器件FPGA为处理核心设计的嵌入式结构产品 ,具有低成本、高集成度、低功耗、小封装等优点,并且其在线编辑具有很高的灵活度,后期升级维护也非常简单。常用的FPGA芯片如Virtex系列,是一种高密度、大容量的现场可编程门阵列芯片,其逻辑单元多达100万个,可兼容16种高性能接口标准,最高工作频率可达200MHZ。Virtex系列FPGA的逻辑文件加载方式由FPGA内部的模式选择信号M[2:0] 的电平来决定[1],常见的加载模式包括JTAG模式、串行模式和并行模式。其中串行模式包括Master Serial和Slave Serial两种,并行模式也分Master SelectMap和Slave SelectMap两类。这些模式的选择与M[2:0]的对应关系见表1。

其中JTAG加载模式中,不需要存储芯片介入,该模式主要用于逻辑文件烧写和调试阶段,在产品断电后需要重新进行加载。串行模式需要使用到的FPGA加载信号较少,通常由FPGA在CCLK的上升沿接收1位数据进行加载,该加载方式速度较慢。而并行模式是一种8位数据加载模式,配置加载时钟最可达66MHz,每个加载时钟周期内有8位配置数据下载到FPGA内。在对加载速度要求较高的一些应用场合,一般采用并行加载模式。本文主要分析了Slave SelectMAP并行模式的逻辑文件加载流程,并对该模式逻辑加载中常见故障进行了分析研究,为基于FPGA的嵌入式产品故障排查提供了理论支持。

2 基于Slave SelectMAP模式的逻辑加载流程

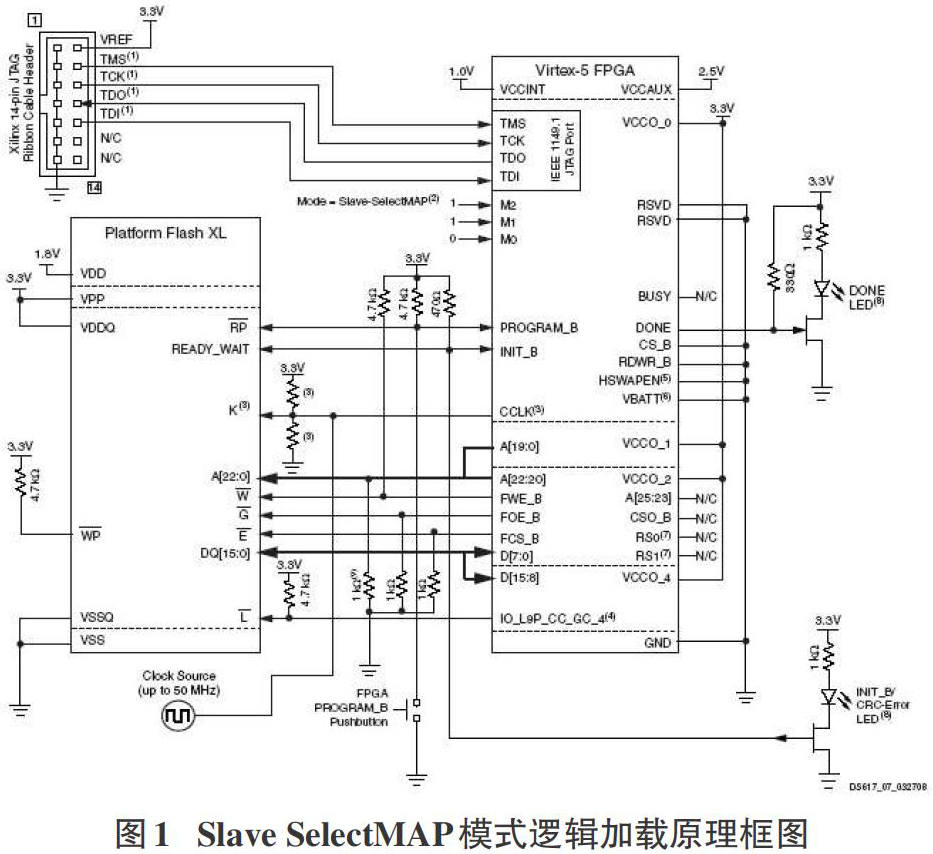

Virtex系列FPGA采用SRAM工艺,FPGA本身具有易失性, 产品下电以后FPGA内部的逻辑文件就会丢失[2], 因此需要外接存储器来保存其逻辑配置数据。图1给出了Virtex系列FPGA基于Slave SelectMAP模式的逻辑加载电路,选取一片专用的Platform Flash存储芯片用以存放逻辑文件[3]。

在逻辑加载过程中,图1中的Virtex系列FPGA为主控设备,左侧的存储芯片为从设备,FPGA发出控制信号从存储芯片中读取逻辑文件,完成加载过程。具体的加载步骤如下:

1)设备上电。在逻辑加载过程中,根据手册要求,设备管脚在加电电源正确时,加载过程才能正常工作;

2)设备初始化及加载模式采样。初始化过程如下:

(1)FPGA完成内部接口上电初始化后,发出PROGRAM_B信号,复位存储芯片,存储芯片发出READY_WAIT低有效信号,表明还在初始化中;

(2)当FPGA完成上电配置,结束PROGRAM_B信号后,并且存储芯片也完成自身初始化后,存储芯片释放READY_WAIT信号(Open-Drain状态),此时INIT_B信号(即存储芯片的READY_WAIT)由外部电阻上拉至高电平状态;

(3)当INIT_B拉高后,设备在加载时钟的上升沿,对特定地址信号管脚M[2:0]进行采样,[0,1,1]表示Slave-SelectMAP加载模式,采样后开始逻辑加载过程。

3)加载过程。配置完成后,设备开始逻辑文件的加载过程,具体过程如下:

(1)对加载设备ID进行校验检查,防止设备错误;

(2)在时钟信号、片选、读信号的控制下,驱动相应单元有效数据至地址总线DO[15:0],并按照CCLK时序完成加载数据传输操作;

(3)完成全部邏辑数据的加载,并且数据CRC校验正常,FPGA发出DONE信号,表明逻辑加载操作成功。

常用的Slave SelectMAP加载模式和JTAG加载模式使用的主要信号见表2。

3 基于Slave SelectMAP模式的逻辑加载故障分析

3.1 加载控制信号错误导致逻辑加载故障

在某产品逻辑加载故障后,使用示波器测量FPGA发出的控制信号,测试结果如图2,图中绿色线为PROGRAM_B信号,蓝色为INIT_B加载控制信号。结果显示,FPGA能够正常输出PROGRAM_B信号,但INIT_B加载控制信号异常,发现INIT_B加载控制信号无法拉高。

结合上文分析过程,INIT_B加载控制信号需要在PROGRAM_B信号变为高电平后,0~3ms内变为高电平才能正常进行逻辑加载。照手册要求,存储芯片完成初始化后,该信号应该由外部电阻上拉至高电平(2.5V以上),而实际测试该信号时钟始终为低电平(0.8V以下),表明存储芯片不能正常完成上电初始化,达到正常状态,所以后续FPGA逻辑加载操作不能启动。

3.2 加载地址线信号错误导致逻辑加载故障

在某产品逻辑加载故障后,编写测试程序对存储芯片进行逐行写入,并读出写入数据。读写结果如图3所示,根据测试程序,通过比较正确状态地址故障态地址,发现是存储芯片地址线A19发生错误,由0偏转为1。经清查,发现该存储芯片管脚脱焊,导致地址线信号错误,FPGA从存储芯片中加载逻辑文件时故障。

3.3 Slave SelectMAP模式能够加载,JTAG模式加载故障

某产品逻辑能够正常加载,但使用外部仿真器在JTAG模式下无法重新加载逻辑文件。根据故障现象及表2中罗列的信号对比可知,在Slave SelectMAP加载过程中,不使用地址线信号及写有效信号,JTAG模式加载时需要从A0地址开始写入数据。经测量,写有效信号常高,导致逻辑虽然能够正常加载,但JTAG模式写入逻辑文件时故障。

4 总结

本文对基于Slave SelectMAP模式的逻辑加载模式进行了研究,分析了加载过程中主设备FPGA及从设备存储芯片各信号的定义和使用情况。结合加载流程和信号分析,研究了三种SelectMAP模式下逻辑加载的典型故障,对FPGA产品故障快速定位提供理论依据和技术指导。

参考文献:

[1] 郭天天.Virtex系列FPGA的SelectMAP配置接口电路[J].微处理机,2000,21(4):17-19.

[2] 瞿海妮.基于单片机的Virtex-ⅡFPGA SelectMAP模式的配置方法[J].微计算机应用,2005(4):463-465.

[3] UG438,Platform Flash XL Configuration and Storage Device User Guide,2009.

【通联编辑:代影】

- 浅谈如何在少年儿童中开展戏剧教育

- 浅谈戏曲表演艺术的特点

- 谈二胡快弓演奏技巧

- 舞蹈编导创造性思维能力的培养策略探究

- 浅析夏之咏叹——《一抹夕阳》

- 以审美为核心的音乐教育改革

- 美声唱法在我国音乐剧演唱中的运用研究

- 感悟作曲家王志信先生的音乐表现及艺术处理

- 论欣赏教学在音乐教育中的地位与作用

- 芭蕾训练在空乘专业形体训练中的作用

- 简析歌剧《伤逝》秋之咏叹——《风萧瑟》

- 浅析话剧表演中人物形象的塑造

- 朱良镇艺术歌曲的创作风格概述

- 关于音乐欣赏中审美体验的养成

- 浅谈话剧表演艺术

- 舞蹈表演中的角色塑造元素探讨

- 再论芭蕾的中国化

- 现代舞的思想架构与身体语言的多面呈现

- 《九歌》中的文化符号观

- 浅谈中国古典舞身韵审美性、训练性、运用性的价值

- 浅析文化艺术修养对声乐作品创新的重要性

- 关于钢琴视奏能力提高的几点建议

- 数字化媒体舞蹈的审美倾向

- 小学生写错别字的原因分析及预防浅谈

- 篆书条幅《游金山寺》创作说明书

- taxers

- taxes

- '-taxes

- taxevasion

- taxexemption

- tax exemption

- taxexile

- tax exile

- tax eˌvader

- tax eˌvasion

- taxfavoured

- taxform

- tax form

- tax-free

- taxfree

- tax free

- tax haven

- taxhaven

- tax holiday

- taxholiday

- taxi

- taxied

- taxies

- '-taxies

- taxiing

- 鬡

- 鬢

- 鬣

- 鬣剪髻

- 鬣狗

- 鬣般

- 鬣葵

- 鬣蜥

- 鬤

- 鬤鬤

- 鬥

- 鬥口

- 鬥叶

- 鬥智

- 鬥牌

- 鬥草

- 鬥鸡走狗

- 鬦

- 鬧

- 鬨

- 鬩

- 鬪

- 鬬

- 鬭

- 鬮