摘 要:针对传统通信系统传输损耗高、抗干扰能力弱的不足,以及传统1B/2B编码难以满足光纤通信的要求,本文融合光纤通信和FPGA可编程技术,设计了基于FPGA的光纤通信系统。重点研究了直流平衡8B/10B编、解码技术及其FPGA实现,并对编解码器进行了验证。最后通过系统仿真及测试,验证了系统功能正确,实现了数据在光纤介质中可靠传输。

关键词:光纤通信;FPGA;数据传输;编码

随着信息化步伐逐渐加快,光纤通信技术已成为现代通信的重要支柱。光纤通信具有传输损耗低、传输频带宽、抗电磁干扰等优点,光纤传输损耗几乎比同轴电缆低三个数量级,并且在整个频段内其损耗对于任何调制信号都相同,因此光纤成为一种理想信号传输媒介[1]。FPGA具有时钟频率高,内部时延小,运行速度快的特点,适于大数据量的高速传输控制[2]。目前,在高速光纤通信中还多采用专用的ASIC 芯片,FPGA的可编程特性,具有ASIC 芯片无法比拟的优越性[3]。因此,本文融合光纤通信和FPGA可编程技术,对基于FPGA的光纤通信系统进行研究,这具有重要现实意义。

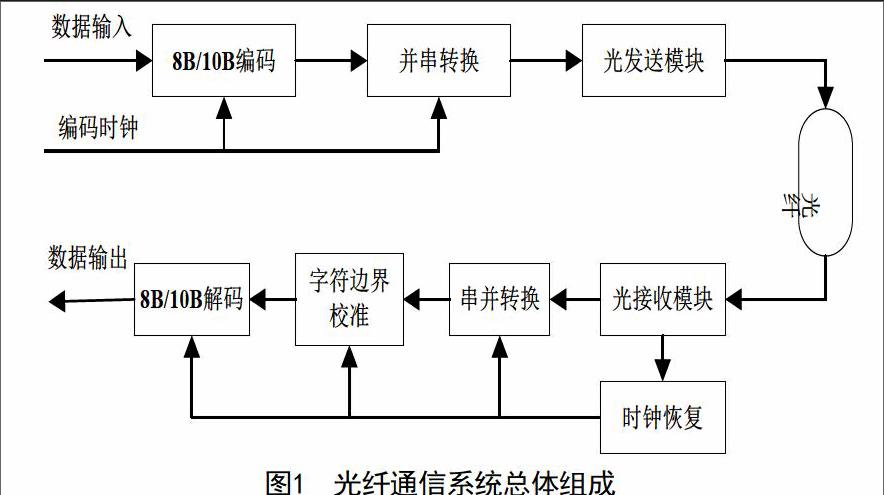

1 系统总体设计

系统主要由时钟模块、8B/10B编解码器模块、串并转换模块和光发收模块组成,主要功能框图如图1 所示。在发送端,并行数据由系统控制送入8B/10B编码器,编码后的10位并行信号经并串转换串行化后差分输出,再由光发送接收模块转换为光信号送入光纤传输介质。在接收端,光接收模块把将接收到的光信号还原回电平信号,时钟恢复模块从串行信号中提取时钟信息,完成最佳采样。串并转换模块将串行信号转换成10位并行数据,然后通过字符边界校准模块调整字边界,再经解码还原为正确的8位数据。

2 直流平衡8B/10B编解码的FPGA 实现

传统1B/2B编码帧之间不可避免出现长0长1,此种高低电平的跳变速率使得接收的光纤信号等效为高阻态导致没有信号,难以满足光纤传输要求。此外,編码中一旦有传输错误易产生错误累积。

8B/10B 编码作为高性能的串行数据编码标准,其主要思想是利用映射机制将一个字节宽度的数据转化为10位宽度的字符,具有直流平衡特性[4]。该编码规定位流中0或1的最大游程长度值不能大于5,使得传输过程有足够高的信号变换频率,保证串行数据在接收端被正确还原,可附用特殊码(K码)进一步确保数据复原。另外,可在早期发现数据位传输错误以抑制错误累积[5]。因此,这些特性使得8B/10B编码特别适合光纤介质的连接和信息传输。

2.1 直流平衡8B/10B编码实现

通信适配接口的输入由单字节数据、控制信号以及时钟信号组成。输入的8bit数据(HGFEDCBA)编码时,将低5位(EDCBA,用x表示)经5B/6B编码成为6 bit(iedcba)码字,高3位(HGF,用y表示)数据经3B/4B编码成为4 bit(jhgf)码字,进而组合得到10 bit码字(abedeifghj)。在8B/10B编码中,包括普通数据字符(用Dxy表示)和特殊控制字符(用Kxy表示)。极性偏差RD(Running Disparity)作为8B/10B编码中重要的概念,是维持编码直流平衡的核心。用RD+表示编码结果中0的大于等于1的个数,用RD-来表示编码结果中1的个数大于等于0的个数。disp表示编码结果中1和0的个数差,4bit编码码组中,disp为0时则为完美平衡码。

8B10B编码顶层原理图如图2所示。数据分离模块将输入8bit数据拆成高3bit、低5bit,同时将整体8bit分别输出。特殊符号编码模块完成特殊控制符号Kxy编码,输出当前编码不均等性disp_k ('0'均等,'1'不均等)。5B/6B编码模块完成5B到6B的编码,输出当前编码不均等性disp_6,其中IsS表示出当前编码是否为5B码。3B/4B编码模块完成3B到4B的初步编码,输出当前编码不均等性disp_4,其中IsOne表示当前编码是否为单值输出,用于合成10B码时判断4B码是否取反。3B/4B编码调整模块根据disp_6和IsOne判断当前3B4B编码输出是否需要反转和调整。RD控制模块将编码后的10 bit数据进行选择输出,同时根据前3个模块输送来的disp_6、disp_4及disp_10来更新当前RD值以反馈到下一轮RD的输入。

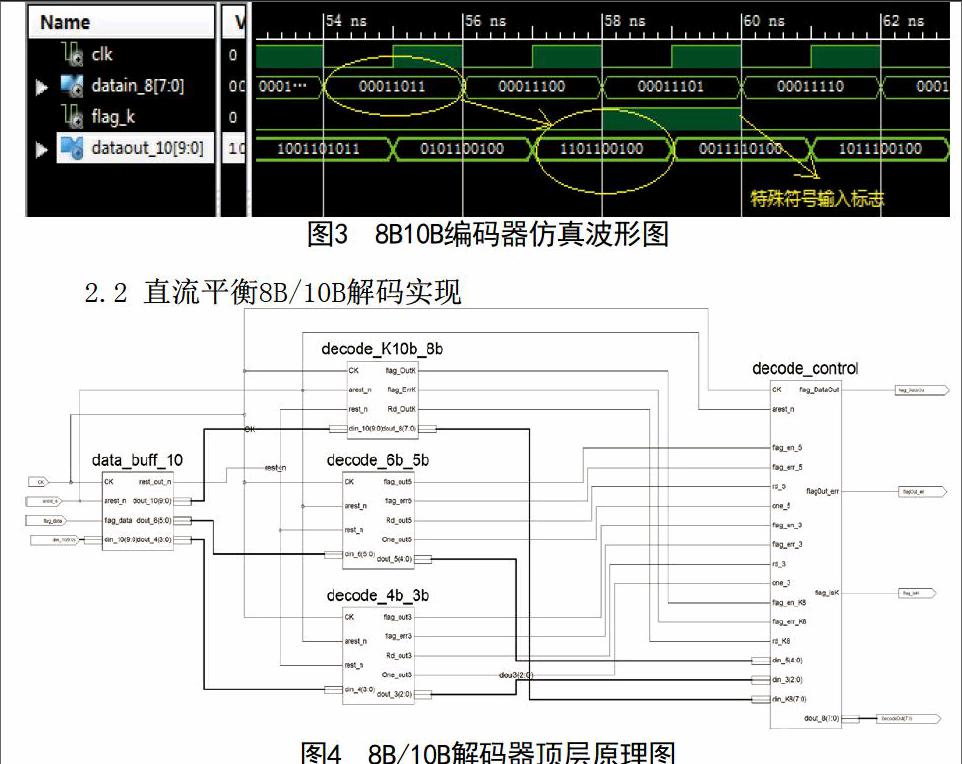

8B/10B编码器仿真波形如图3所示,可知8bit数据00011011被编码成为10bit数据1101100100。输入为00011101的特殊控制码被编码为1011100100。编码结果与查码表一致,表明该编码器实现了正确编码。

2.2 直流平衡8B/10B解码实现

解码模块顶层原理图如图4所示,解码器由块数据缓存,特殊符号解码,3B/4B解码,5B/6B解码以及解码控制模块组成。系统检测到标志位flag_out为1时进行解码,先判断接收码,若为特殊控制码则直接查找表解码。否则,将接收的10位码分解为高6位和低4位,高6位用5B/6B的查找表解码得到5bit码,低4位用3B/4B的查找表解码得到3bit码,最后将得所3bit码为高位而5bit码为低位重新组合成8bit码。图4中的输出信号包括:Dout_8为8bit解码,flag_DataOut为输出有效信号,flag_IsK为特殊控制码,flagOut_err表示解码错误。8B/10B解码仿真波形图如图5所示,图中din_10为输入的10bit的数据,decodeout为解码的数据。图中给出了K23.7,D0.0,D1.0,K27.7的正确解码。

3 系统功能验证及测试

系统完成后,为验证输出数据的正确性,预设输入模块循环往发送端输入FIFO里输入00到01,此时接入示波器以观察输出波形。另外,将发送模块最终的编码串行输出连至接收端的串行输入口,为了直观观测数据,在输出异步FIFO后连接UART至PC机串口,通过串口助手观测接收码。系统仿真波形与示波器实测波形对比如图6所示,由结果可知,系统仿真结果与实测信号相符,验证了系统功能正确性。另外,串口助手不停的接收整齐的00,01数据,进一步验证了信号在实际传输时的正确性。

4 结语

本文研究并实现了基于FPGA的光纤通信系统。通过仿真和实验,实现了数据在光纤内的可靠传输,验证了系统功能正确。相对于传统通信系统,具有传输速率高,传输带宽宽,抗电磁干扰能力强等优点。本设计也可用于其它串行高速传输通信系统,此外,在8B/10B编码时运用特殊控制码,配合多个FIFO收发端,组成不同结构的数据链路网络,实现多种数据的汇总和传输。

参考文献

[1] 陈克难,刘文红.使用光纤传输信号波形的技术[J].仪器仪表学报, 2005, 26(z1):537-538.

[2] 秦奎,张卫平,陈文元.基于ARM和FPGA的微加速度计数据采集系统设计[J].现代电子技术,2010,313(2):25-27,30.

[3] 李欣,管绍军,胡晓天.基于FPGA的光纤通信系统的设计与实现[J].电子设计工程, 2012,20(8):85-87.

[4]秦蒙,王辉,秋云海,等.光纤通信中8B/10B编码器的设计与实现[J].电视技术, 2014, 38(1):50-54

[5]李玉伟,潘明海. 8B/10B编码对高速传输的影响分析[J].信息安全与通信保密, 2011(3):41-43.

- 主塔施工技术及质量控制措施

- 桥涵施工中常见缺陷分析

- 工业厂房内工艺管道安装技术工艺研究

- 浅谈桥梁检测技术

- 关于刚性整体吊弦运行状态的探讨

- 广告设计中色彩应用初探

- 房建施工中绿色施工技术的应用浅析

- 公路工程施工现场管理研究与探讨

- 城市步行街区人性化规划设计方法研究

- 建筑机电安装施工质量技术分析

- 加强建筑项目管理,提高建筑工程建设效益

- 农村消防安全工作及其对策

- 土木工程施工管理及质量控制研究

- 公路路基工程质量常见问题的解决

- 钻孔灌注桩质量保障措施及其通病分析

- 工程施工中质量监理工作研究

- 水下振冲碎石桩单桩承载力计算方法研究

- 高速公路桥梁墩台处边坡病害探讨

- 城市规划对建筑环境影响分析

- 水泥混凝土路面施工应注意的问题

- 路桥施工常见病害和对策分析

- 工程预决算中若干问题探讨

- 桥梁大体积混凝土裂缝控制措施

- 市政道路路面的结构设计及病害防治措施

- 浅议火灾自动报警系统设施

- daydreamy

- daydream²

- daydream¹

- day-glo

- day-in-and-day-out

- day in, day out

- dayless

- daylight

- daylighted

- daylights

- daylit

- day off

- dayoff

- day off/afternoon off etc

- day one

- day order

- dayorder

- day out

- dayrate

- day rate

- dayrelease

- day release

- day return

- day returns

- days'

- 外合里应

- 外向

- 外向力

- 外向双语词典

- 外向型

- 外向型企业

- 外向型经济

- 外向度

- 外向性

- 外向意识

- 外向结构

- 外君子而内小人

- 外听道

- 外呈和善之貌,内存害人之心

- 外命妇

- 外命婦

- 外和

- 外哈

- 外商

- 外商投资企业

- 外商独资经营企业

- 外嗽弼

- 外四路

- 外因

- 外因是变化的条件,内因是变化的根据