摘 要: L波段数字航空通信系统(L?DACS1)是一种基于正交频分复用(OFDM)技术的多载波传输方案。该系统具有频谱利用率高、抗多径干扰能力强等优点,适用于信号传输信道更复杂的民用航空地?空通信,并作为未来数字航空通信系统的候选系统之一。研究了L?DACS1系统数字变频器的设计方案,并基于现场可编程门阵列(FPGA)在Apex?CPCI?5610通信开发板上实现了这种方案。测试结果表明,该方案能够正确地实现数字上/下变频,能够满足L?DACS1系统设计要求。

关键词: L?DACS1; 正交频分复用; 数字变频器; 现场可编程门阵列

中图分类号: TN914.3?34 文献标识码: A 文章编号: 1004?373X(2015)03?0059?03

Design and implementation of digital converter in L?DACS1 system based on FPGA

LI Yong, LIU Hai?tao

(Tianjin Key Lab of Advanced Signal and Image Processing, Civil Aviation University of China, Tianjin 300300, China)

Abstract: L?band digital aeronautical communication system (L?DACS1) is a kind of multi?carrier transmission one based on orthogonal frequency division multiplexing (OFDM). The system has the advantages of high utilization rate of frequency spectrum and anti?multipath interferences. It is applicable to civil aviation A/G communication channel which is more complex for signal transmission, and is a candidate of digital aviation communication systems in the future. The digital converter design scheme for L?DACS1 system is investigated in this paper. The scheme based on field programmable gate array (FPGA) was realized in Apex?CPCI?5610 communication development board. The test results show that the scheme can accurately implement digital up/down conversion, and can meet the design requirements of the L?DACS1 system.

Keywords: L?DACS1; OFDM; digital converter; FPGA

0 引 言

为了解决地空的数据传输业务增长而带来的高通信速度要求和高宽带要求问题,欧洲EUROCONTROL提出了未来航空通信系统(FAC)的候选系统,即L波段数字航空通信系统类型1和2(L?DACS1和L?DACS2)。其中L?DACS1系统是一种基于正交频分复用(OFDM) 技术,采用频分双工(FDD)模式,工作在L波段的多应用蜂窝宽带通信系统。提供双向点对点寻址数据链通信,该系统具有频谱利用率高、抗多径干扰能力强等优点,适用于信号传输信道更复杂的民用航空地?空通信[1]。

数字变频器是软件无线电系统中必不可少的一个模块,其作用是实现发射机基带信号的数字上变频及接收机A/D输出信号的数字下变频。本文通过研究L?DACS1协议[2]内容,针对L?DACS1系统的特点,基于Xilinx公司的FPGA开发板平台实现了L?DACS1系统变频器。

1 数字变频器的方案

本设计利用Matlab整定滤波器参数[3],并利用Verilog HDL语言编程,在ISE开发环境下构建系统模型,用ModelSim仿真软件进行仿真验证,最后下载到Apex?CPCI?5610通信开发板的V5芯片中,借助示波器和频谱仪对数字变频器进行进一步验证。

在L?DACS1系统中,基带信号的带宽为249 kHz,采样率为625 kHz,根据系统要求及所用的开发板的性能将基带信号数字上变频到30 MHz的载波上,采样率为150 MHz。

图1显示给出了基带信号数字上变频到中频30 MHz的步骤框图。基带输出的信号采样率为625 kHz,由625 kHz的采样率变为150 MHz的采样率,采样倍数提高了240倍。本设计中选择的上变频方案为:首先经过4级半带滤波器的内插使采样率变为10 MHz,实现低速率的内插;再经过一个FIR滤波器的3倍内插,采样速率变为30 MHz;最后经过一个适合在高采样率条件下工作的CIC滤波器的5倍内插,采样率变为150 MHz,同时调用DDS IP核,产生频率为30 MHz,采样率为150 MHz的正余弦信号,分别与Q路和I路信号相乘,将两路信号的相乘结果相加并经过D/A变换便得到30 MHz的中频信号。

图2显示给出了中频30 MHz信号数字下变频到基带信号的步骤框图。与数字上变频相反,采样速率降低240倍,本设计中选择的方案为:中频信号经过A/D变换后分别与本地载波信号相乘,产生I和Q两路基带信号,首先经过CIC滤波器的5倍抽取,采样速率变为30 MHz;之后再经过CIC的6倍抽取,采样率变为5 MHz;以上两个CIC滤波器实现了前端抗混叠的抽取,此时采样率降到了较低的频率,最后再经过3级半带滤波器的抽取即可得到采样率为625 kHz的基带信号,由于半带滤波器工作在较低的频率下,且滤波器的参数得到了优化,更容易以较低的阶数实现。

2 数字变频器的设计与实现

2.1 NCO的设计与实现

在数字变频器中,本地震荡信号是通过DDS(Direct Digital Frequency Synthesis)产生的[4]。DDS的基本原理是利用采样定理,通过查表法产生波形,DDS的结构有很多种,其基本的电路原理如图3所示。

式中:[D]为抽取系统总的抽取(内插)因子。在本设计中,设计系统的通带容限和阻带容限均为0.001。

3 系统的建模与仿真

为了验证数字变频器的正确性,本设计中,对变频器输入一个频率为125 kHz,采样率为625 kHz的正弦波,用ModelSim对变频器进行仿真:

图6给出了在激励信号的作用下,变频器的时序仿真图。由于I,Q两路的模块是一样的,在此只看I路。其中第一路是输入的激励信号源采样率为625 kHz;第二路是经过数字上采样的信号,采样率变为150 MHz;第三路是经过数字上变频输出的中频信号;第四路是数字下变频输出的基带信号,采样率为625 kHz。由图6可以观测出,变频器正确地实现了数字上下变频。

图6 系统时序仿真图

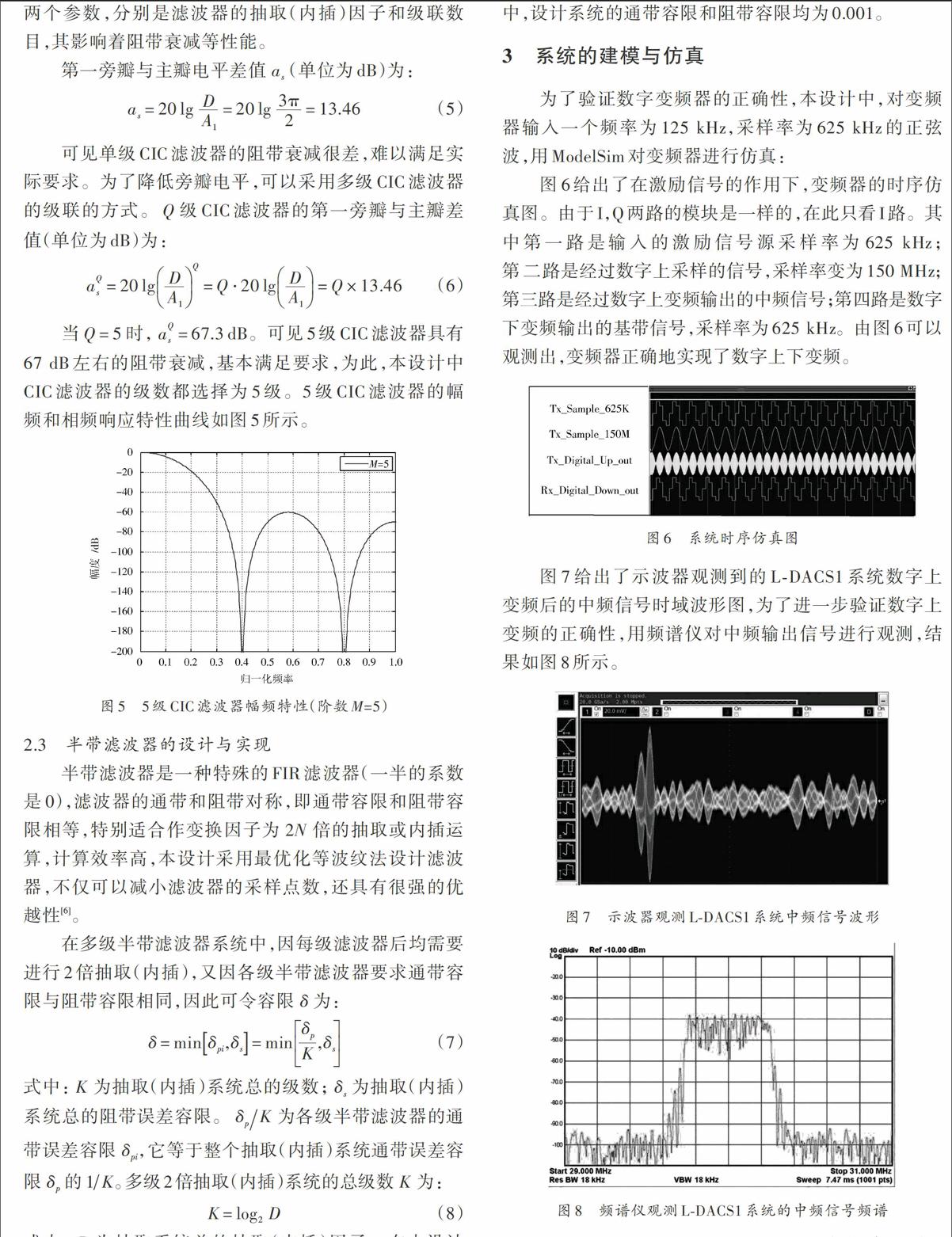

图7给出了示波器观测到的L?DACS1系统数字上变频后的中频信号时域波形图,为了进一步验证数字上变频的正确性,用频谱仪对中频输出信号进行观测,结果如图8所示。

图7 示波器观测L?DACS1系统中频信号波形

图8 频谱仪观测L?DACS1系统的中频信号频谱

图8显示的是频谱仪观测的L?DACS1系统数字上变频后信号的频谱图。由图8可以观测出,频谱的宽度是498 kHz,中频在30 MHz,符合L?DACS1设计规范,进一步验证了数字上变频的正确性。

4 结 语

数字变频器是整个软件无线电中最为关键的信号处理模块之一,本设计采用模块化的思想,对变频器的整体设计方案进行不断优化,同时对数字振荡器、CIC滤波器、HB滤波器等模块建立模型,不断地仿真和验证,修改参数滤波器参数,最后建立了性能最佳的数字变频器。把数字变频器应用到L?DACS1系统中,实现了整个系统的正确传输,取得很好的效果,因此本设计具有较高使用价值。

参考文献

[1] 罗银辉,张欢.民航宽带数据链技术研究进展[J].数字技术与应用, 2011(8):80?81.

[2] SAJATOVIC M, HAINDL B, EHAMMER M, et al. L?DACS1 system definition proposal: deliverable D2 [M]. [S.l.]: Eurocontrol, 2009.

[3] 徐小明,蔡灿辉.基于FPGA 的数字下变频(DDC)设计[J].通信技术,2011,44(10):19?24.

[4] 丁小峰,韩方景,王振伟.基于FPGA和DDS数字调频发射机实现[J].电声技术,2006(9):64?66.

[5] 杜勇,陆建功,李元洲.数字滤波器的Matlab与FPGA实现[M].北京:电子工业出版社,2012.

[6] 黄静月,田克纯,常博学.一种基于FPGA的高效数字上变频的设计与实现[J].器件与电路,2011,35(9):27?30.

- 信用评级、法律依托与农村电子商务风险

- 我国农村电子商务发展现状、问题及对策研究

- 长江经济带农产品流通效率的时空特征及因素分解

- 西北欠发达地区农产品区域品牌问题研究

- 人力资源服务产业园建设问题研究

- 创新创业导向下地方高校电子商务人才培养模式研究

- 女性优秀人才的生态开发与国家软实力建设浅论

- 新时代高校审计专业教师创新创业教学能力构建研究

- 基于游客满意度的五台山旅游发展研究

- 论财政监督检查中存在的问题及改进方法

- 输配电价改革下的会计管制制度设想

- 大数据时代医院财务管理创新发展研究

- 基于大数据背景下财务数据和业务数据的融合

- 中国工业绿色全要素生产率的空间差异

- “健康中国”战略下河南省健康养老产业发展路径选择

- 银行支持山西省文化旅游产业发展探析

- 西部地区劳动生产率对就业增长的非线性效应研究

- 基于扎根理论的创意产业集群空间集聚影响因素研究

- 景德镇陶瓷文化产业创新能力的进化路径研究

- 黑龙江省冰雪产业发展对策研究

- 我国村镇银行发展现状、挑战与对策研究

- 对房地产金融潜在风险的分析与思考

- 浅谈出口信用保险在国际工程中的作用

- 大型国企的分拆上市之路

- 浅析影响金融风险传染的因素

- intermuseum

- intern

- internal

- internalaudit

- internalconsistency

- internalconsultancy

- internalcustomer

- internalequity

- internalities'

- internalities

- internality's

- internallabourmarket

- internally

- internalmarket

- internalness

- internalnesses

- internalness's

- internal rate of return

- internalrateofreturn

- internalrevenuecode

- internalrevenueservice

- internals

- internal's

- internalsearch

- internation

- 进行战争

- 进行战斗

- 进行战斗的原则和方法

- 进行打击迫害

- 进行抢劫

- 进行持续的具体努力

- 进行挽救为时已晚

- 进行政治上的改良

- 进行教学

- 进行教学活动之所

- 进行教学活动,传授知识

- 进行斗争的工具

- 进行曲

- 进行曲之王

- 进行杂技表演

- 进行极其秘密的谋划

- 进行欺骗

- 进行武装叛变的军队

- 进行残酷的剥削勒索

- 进行残酷的压榨和剥削

- 进行比较和推测

- 进行深入思考和长远考虑

- 进行激烈战斗

- 进行煽动性的活动

- 进行犯罪活动