摘 要: 以纳卫星研究项目为背景,设计和实现了适用于纳卫星的新型发射机。该发射机具有功耗低、重量轻、体积小、灵活性高等特点。根据指标要求,理论计算发射功率要求,研究发射机的结构,并详细讨论芯片选型。星载发射机的基带处理部分由现场可编程门阵列(FPGA)实现,完成信道编码、扩频、BPSK调制;输出采样经过数/模转换、滤波网络、正交调制、功率放大、功率分配等模块后,通过天线辐射出去。设计了FPGA软件,完成外部使能检测、芯片在线配置和BPSK调制。在一块印制电路板上实现发射机设计,最后通过实际地面测试,功耗约为2.5 W,重量约为16 g,尺寸为80 mm×38 mm×15 mm,发射功率为24 dBm,表明设计结果满足尺寸、重量、发射功率等指标要求。

关键词: 纳卫星; 发射机; 扩频; FPGA; BPSK

中图分类号: TN836?34 文献标识码: A 文章编号: 1004?373X(2015)07?0064?05

0 引 言

纳卫星(Nano?satellite)是以微机电系统(MEMS)技术为基础的一种全新概念的微小卫星,质量在10 kg以下,1 kg以上[1?2]。与大卫星相比,纳卫星具有集成度高、体积小、质量轻、功耗低、研制周期短、成本低、机动性强等特点。通过分散式的星座结构组网,纳卫星可以实现甚至超越一颗大卫星的功能,并且能以较低的成本实现卫星搭载和空间新技术演示等科学实验项目[3]。因此纳卫星在科学研究和商业应用领域都将发挥重要作用。

本文研究目标纳卫星总体重量约为2 kg,其本体结构为20 cm×20 cm×20 cm的立方体。整个纳卫星由通信系统、计算机控制系统、电源系统、姿测与姿控系统、空间相机和有效载荷等部分组成。卫星表面安装有太阳能电池、天线和相机镜头等设备。

在纳卫星中,通信系统主要负责纳卫星与地面的信息交互工作。星载发射机作为通信系统中不可或缺的一部分,其设计原则不同于传统卫星发射机,受到了功耗、体积和重量等技术指标的严格限制。同时,限于纳卫星的自身条件,星载发射机必须在满足数据传输速率和发射功率要求的前提下,尽可能地减小体积和降低功耗。本文根据纳卫星的特点,设计了一种新型星载通信发射机,并在地面试验中验证了其功能和性能指标。

1 星载发射机技术指标及发射功率设计

星载发射机主要完成纳卫星下行数据的发送。根据国际相关微小卫星设计惯例,发射机载波频段为2 200~2 400 MHz,拟采用的载波频率为2 323 MHz。发射机待传送的数据包括图像数据和卫星状态数据,数据速率设计指标为1 024 b/s。待发送数据经过扩频、BPSK调制上变频后通过天线辐射出去;要求接收端的误码率低于[10-6]。

根据以上星载发射机的各项技术指标,下面对发射功率进行论证。

1.1 星载发射机发射功率的确定

为保证接收机能正确接收和解调纳卫星发送的BPSK信号,星载发射机的最小发射功率可以表示为:

[PT=LP-GR+LF+Pmin] (1)

式中:[LP]为信号在自由空间中的路径损耗;[GR]为接收天线增益;[LF]为馈线及其他损耗;[Pmin]为接收机的灵敏度。对于信号的路径损耗[LP]可以计算为:

[LP=32.4+20log(f)+20log(d)] (2)

式中:[f]为发射机发送的载波频率,单位为MHz;[d]为发射机到地面接收机的空间距离,单位为km。本设计中纳卫星到地面站的测控距离为1 877 km,载波频率为2 323 MHz,代入式(2)中可得[LP=165.2]dB。

设接收天线增益[GR=30]dB,馈线及其他损耗[LF=]5 dB。分析接收机的灵敏度[Pmin。]由于星载发射机采用了扩频调制,地面扩频接收机灵敏度可以计算为:

[Pmin=NF+kT0BRF+(EbNo)min-PG] (3)

式中:[NF]为接收机的噪声系数;[k=1.38×10-23 ]J/K为波尔兹曼常数;[T0]为接收机端的绝对温度,设为室温293 K;[BRF]为射频信号带宽;[(EbNo)min]为接收机允许的最小信噪比;[PG]为扩频系统的处理增益。

本文所设计的星载发射机采用直接序列扩频(DSSS),根升余弦滚降滤波,再通过双相移位键控(BPSK)对载波进行调制。原始数据速率为1 024 b/s,扩频码速率为1.023 Mb/s,扩频增益[PG=29.995 8]dB。

由通信原理相关知识可知,假设传播信道为AWGN,BPSK调制下误码率(BER)和信噪比([EbNo])之间的关系如图 1所示。由图 1可知,当接收机误码率要求低于[10-6]时,[(EbNo)min=10.5]dB。

进一步,设噪声系数[NF=1.6]dB,因此,可以计算出接收机的灵敏度[Pmin=-128.7]dBm。

综上所述,发射机的最小发射功率应为:[PT=LP-GR+LF+Pmin=11.5 dBm] (4)

而对于实际的通信系统,采用合适的信道编码方案约有7 dB的编码增益[4],系统要求保持15 dB的链路余量和2 dB左右的解调损耗,故星载发射机最终的发射功率设计值为21.5 dBm。

图1 BPSK调制下BER和SNR之间的关系

1.2 星载发射机硬件设计及芯片选型

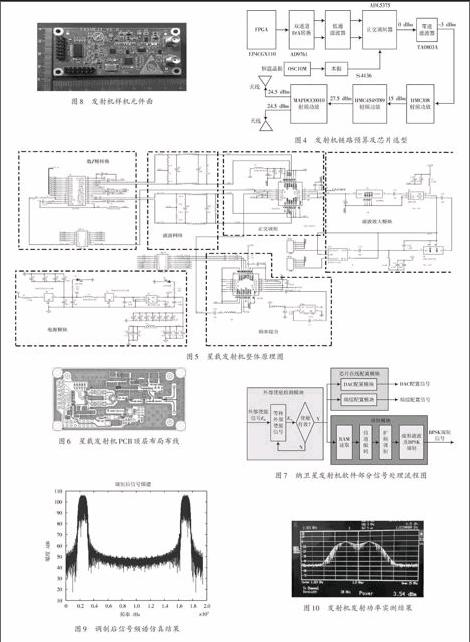

基于纳卫星星载发射机的特点,采用模块化设计,主要包括数/模转换、频率综合、正交调制、滤波放大和电源5个模块,其结构框图如图2所示。

图2 星载发射机结构框图

数/模转换模块接收FPGA送来的10位总线数据,将其转换为两路模拟差分信号输出;滤波网络完成带外噪声抑制;正交调制模块利用频率综合模块输出的载波信号对模拟信号正交调制上变频;射频信号经过带通滤波和两级功放后再由功率分配器分配到两个天线辐射出去。

结合1.1节发射机最小发射功率设计结果,星载发射机各个模块的芯片选型说明如下:

1.2.1 数/模转换模块

数/模转换模块选用Analog Devices公司的AD9761芯片,单路输入,差分输出,可以满足对PFGA输出的单路BPSK数字信号的数/模转换。

AD9761可以完成10位中等精度双通道数据的处理,差分非线性误差小,采样速率高达40 MSPS,紧缩小封装SSOP?28,占用面积小,3~5.5 V单电源供电、最大功耗仅97 mW,同时,外围硬件设计相对简单,便于在星载发射机上实现。

1.2.2 频率综合模块

频率综合模块采用Silicon Laboratories公司的完整频率合成器芯片Si4136。该芯片产生的时钟稳定性高,精度高,可以满足正交调制模块对载波频率的要求。

Si4136外部选用10 MHz恒温晶振作为参考时钟,其内部由1个中频锁相环、1个22位数据寄存器、2个射频锁相环、3个压控振荡器(VCO)及三线控制器组成,内部结构功能框图如图3所示。Si4136为双频段射频综合器,可以输出射频频段RF1:2 300~2 500 MHz和RF2:2 025~2 300 MHz。通过FPGA对使能信号SENB、时钟信号SCLK和数据信号SDATA的配置,可以对输出频率进行控制和修改[5]。芯片的电源电流典型值为25.7 mA,电源电压为3.3 V,具有功耗低,相位噪声小等优点。

1.2.3 正交调制模块

正交调制模块采用Analog Devices公司的ADL5375芯片实现宽带正交调制,具有优异的载波抑制和边带抑制性能,带宽利用率高,抗干扰能力强,满足系统需求。

ADL5375将DAC输出的两路差分信号调制到本振信号上。要采用24脚LFCSP_VQ小型封装,4.75~5.25 V单电源供电,工作频率范围为400 MHz~6 GHz,调制器的输出功率在0 dBm左右。

1.2.4 滤波放大模块

滤波放大模块由带通滤波器、两级功率放大器和功率分配器三部分组成。

带通滤波器采用射频带通滤波芯片TA0803A,消除带外频率分量对载频的影响。TA0803A的中心频率为2 313.5 MHz,带宽为27 MHz。本文设计的发射信号在TA0803A通带频段2 286.5~2 340.5 MHz内,频段内阻带可衰减32 dB,能够对带外频率进行有效抑制。带通滤波器的插入损耗为3 dB,故滤波器的输出功率约为-3 dBm。

由于滤波输出功率远远达不到发射机要求的最小发射功率23.5 dBm,因此在发射机的末级采用了射频功率放大器以达到预算目标功率。

本文采用两级级联的功放。第一级的作用是保证信号被线性地放大,在此基础上力求高效率;第二级的作用是在提高效率的前提下尽可能满足一定的线性要求[6]。第一级功放选用HMC308,其线性放大效果明显,增益达18 dB,可以实现15 dBm的功率输出;第二级选用HMC454ST89,效率高,增益12.5 dB,输出功率为27.5 dBm,满足发射功率要求,且余量较大。

由于纳卫星在空间可能发生翻滚,为增加地面接收机接收到信号的概率,在纳卫星的相对两面分别配置一个天线。因此,需要选择一个功率分配器,将信号分配到两个天线上辐射出去。功率分配器选用MAPDCC0010芯片,其插入损耗为3 dB,两路输出功率均为24.5 dBm,其比发射功率设计值大3 dBm,可以满足接收机对解调和误码率的要求。

1.2.5 电源模块

电源模块是发射机最重要的部分,稳定且高效的电源才能够保证整个系统稳定工作,不会因为电源波动影响整个系统的运行。本文中选用的电源芯片为MIC5245?3.3 V。在纳卫星星载发射机中输入电压为5 V,其他模块使用的电压仅有5 V和3.3 V,压差较小。而传统的DC?DC芯片需要输入电压比输出电压高出2 V以上才能正常工作,因此不能采用。MIC5245?3.3 V是低压差稳压器,内部采用CMOS晶体管工艺,输入电压与输出电压的差值只需要保持在一个很低的水平(仅200 mV左右);而且该芯片电源转换效率较高,输出噪声小,静态电流小,适合于纳卫星上使用。同时为了减少电源的干扰,选用大电流三端电容器NFM2012P13C104R对电源进行线性滤波。

综上设计,星载发射机的链路预算及芯片选型结果如图4所示。由图4可知,星上发射机发射功率为24.5 dBm,满足发射机所需发射功率21.5 dBm的设计指标。

发射机模块化设计完成后,应用工具Cadence 16.5完成原理图和印刷电路板(PCB)的绘制。星载发射机整体的原理图如图5所示。

根据纳卫星对体积的要求,确定该发射机PCB版图尺寸是80 mm×38 mm,板上四角有机械安装孔,方便发射机的固定。电路板采用四层板架构,分别为:顶层信号层,中间两层接地层,底层信号层。板材选择高频板材Rogers 4350B,厚度为0.8 mm,介电常数为2.55,表面处理采用方式为沉金,符合电路阻抗匹配和信号传输速率的要求[7]。

由于PCB涉及模拟信号和数字信号,基带信号和射频信号,所以将模拟信号和数字信号分区域布置,在空间上隔离以降低串扰风险。由于地线在射频时存在一定阻抗,易形成数/模共阻抗干扰,所以PCB使用长宽比小于3的GND平面,降低GND阻抗,进一步降低共模电压;使用数/模分割,避免数字GND产生的共模电流流经模拟区域。绘制完成的发射机PCB顶层布局布线如图6所示。

图4 发射机链路预算及芯片选型

图6 星载发射机PCB顶层布局布线

最后需要说明的是,本设计中FPGA模块布局在核心板上,以便降低整体功耗,减小重量和尺寸,这里不进行详细说明。

2 星载发射机软件设计

纳卫星发射机的基带处理部分在FPGA内部实现。FPGA芯片选用Altera公司的Cyclone IV EP4CGX110,具有较为丰富的逻辑和存储资源,可以完成数据和流程处理。信号处理的流程图如图7所示。

由图7可知,纳卫星发射机软件部分可分为三个模块:外部使能检测模块,芯片在线配置模块和调制模块。

图7 纳卫星发射机软件部分信号处理流程图

各个模块工作原理简单介绍如下:

(1) 外部使能检测模块

纳卫星在未收到计算机主控模块的数据读取命令之前一直处于低功耗休眠等待状态,在此状态下,后续模块均不工作,可以大大降低纳卫星在发射空闲时间的能耗。若检测到有效的使能信号,则控制后续的芯片配置模块和调制模块开始工作。

(2) 芯片在线配置模块

纳卫星发射板上的数模转换芯片和频率合成器芯片均由FPGA进行配置。配置数模转换芯片为单通道工作模式。通过SPI接口对频率合成器芯片进行配置,输出2 323 MHz载波。

(3) 调制模块

调制模块主要是对纳卫星待传输的信号进行规定的调制,以使其适合在信道中传输,其内部各模块的工作原理描述如下:

① RAM读取。若检测到使能信号有效,则开始对指定块RAM进行读取操作。块RAM中存储的数据包括状态数据和压缩图像数据。

② 信道编码RAM。纳卫星的数据传输距离远,信道条件复杂,可靠性低,采用信道编码可以有效地提高传输可靠性。综合考虑信道及资源情况,可以采用简单的纠错编码方式来实现信道编码。本设计中采用级联码,外码为RS(255,223),内码为卷积码(2,1,7)。在BER为[10-6]时,采用软判决译码可以获得约7 dB的增益[4]。

③ 扩频调制。扩频调制技术因其具有抗干扰性强、易于同频使用和抗多径干扰等优点,广泛应用于卫星通信领域。扩频调制采用DSSS,选用的扩频码速率为1.023 Mb/s,周期为1 ms,扩频增益达29.995 8 dB。

④ 成形滤波及BPSK调制。为防止在接收机端形成码间干扰,基带信号在BPSK调制之前先进行成形滤波,成形滤波器选用根升余弦滤波器,滚降系数[α=0.5。]经过成形滤波后,可计算出调制后信号带宽为[1.023×(1+α)=1.534 5]MHz。BPSK信号是一种恒包络抑制载波双边带信号。该模块在成形滤波后再完成中频调制,然后由后续的正交调制器芯片完成射频调制。其中中频信号采用直接数字频率合成技术(DDS)生成。设计中,FPGA芯片的采样时钟为19.437 MHz,发射机所选用的中频为2.43 MHz,采用位宽为29位的累加器进行相位累加,可得频率分辨率[Δf=20×][106÷229=0.037]Hz。使用FPGA设计DDS,可以在满足系统要求和保持DDS原有优点的基础上,减少硬件复杂性,降低芯片面积和功耗。

3 测试结果及分析

本文设计并完成了具体的电路原理图和电路板,调试了各部分电路,基本达到了预期的目标。纳卫星发射机的基本功能已实现。

图8是本文设计并调试通过的电路板元件面,该电路板重量为15.5 g,本体尺寸为80 mm×38 mm×15 mm,实际测试功耗2.5 W,满足纳卫星的要求。传统的测控应答机体积大、功耗高:国内现有的测控应答机一般功耗在10 W左右,体积大于1 000 cm3。相比之下,星载发射机优势明显。

图8 发射机样机元件面

使用在线逻辑分析仪SignalTap Ⅱ在线对FPGA输出的中频BPSK信号进行采集,频域分析后的仿真结果如图9所示。其中,采样频率为19.437 MHz。由图9中可以看出,信号频谱主包络的中心频率为2.43 MHz,信号带宽约为1.5 MHz,这与理论中心频率与成形后的扩频带宽基本相符,验证了FPGA输出结果的正确性。

图9 调制后信号频谱仿真结果

星载发射机实际发射功率地面试验实测结果如图10所示。为了保证测试仪器的安全性,在天线接口处添加了一个20 dB的衰减器。

图10 发射机发射功率实测结果

由图10可知,频谱的中心频率为2 323 MHz,发射机经过20 dB的衰减器实测功率为3.54 dBm,即输出功率为23.54 dBm,考虑到实际测试中射频泄漏和测量误差,该发射机实测发射功率在误差允许范围内,完全满足纳卫星设计要求。

4 结 语

在体积、重量、功耗等设计约束条件下,本文完成了纳卫星星载发射机发射功率论证、芯片选型、硬件设计和软件设计。地面试验测试结果说明,发射机实现了纳卫星的射频信号发射功能,工作性能稳定,工作带宽较宽,带外抑制较好。而且,该发射机具有功耗低、体积小、结构简单,调试方便的特点,完全满足纳卫星系统的应用要求。

参考文献

[1] NEJI B, HAMROUNI C, ALIMI A M. ERPSat?1 scientific pico satellite development [C]// The 4th Annual IEEE Systems Conference. [S.l.]: IEEE, 2010: 255?260.

[2] GAO S, CLARK K, UNWIN M. Antennas for modern small satellites [J]. IEEE Antennas and Propagation Magazine, 2009, 51(4): 40?56.

[3] 林来兴.分布式小卫星系统的技术发展与应用前景[J].航天器工程,2010(1):60?66.

[4] 由佳彬.串行级联编译码的设计与FPGA实现[D].哈尔滨:哈尔滨工业大学,2011.

[5] 闫文智.基于Si4136的小型化低损耗本振设计[J].科技传播,2012(12):214?215.

[6] 肖婷婷,周东平.两级功率放大器静态偏置点的研究[J].中国集成电路,2008,17(1):51?57.

[7] 吴建辉,茅洁.射频电路PCB设计[J].电子工艺技术,2003,24(1):19?21.

- 关于林业种苗容器育苗技术的探讨

- 以生物防治为主的综合控制我国重大林木病虫害进展分析

- 浅谈乡土植物在园林中种植与应用

- 城市水景设计技术框架与相关对策

- 树木整形修剪的意义和原则

- 池州市水土流失现状及水土保持规划要点分析

- 新型PVC防渗抗冻水渠材料时述

- 蓝靛果机械采收配套栽培农艺技术

- 浅谈高次团粒客土喷播边坡裸岩植被恢复

- 试论农机维修技术与保养问题的处理措施

- 农业机械技术推广在现代农业中的作用

- 关于农业机械的常见故障及预防措施

- 自动导航拖拉机在精准农业上的应用

- 试探机械工程自动化当中的农业智能化技术

- 浅谈种子企业的商业化育种

- 种植技术对农业经济的促进作用

- 探究生态农业中植保新技术的应用

- 成县大樱桃产业现状分析

- 我国土地利用研究进展概述及展望

- 鹿寨县耕地等级变化评价

- 三江侗族自治县土壤及农作物硒含量规律初步研究

- 绿藻对烤烟湿润育苗影响及绿色防控策略

- 推进农产品质量安全追溯体系建设的思考

- 邯郸市永年区土壤耕层肥力变化情况

- 猪粪栽培食用菌研究进展

- encl

- enclave

- enclaved

- enclaves

- enclaving

- enclosable

- enclose

- enclosed

- encloser

- enclosers

- encloses

- enclosing

- enclosure

- enclosures

- encodable

- encode

- encoded

- encodement

- encodements

- encoder's

- encoders

- encodes

- encoding

- encompass

- encompassed

- 无心云

- 无心人对有心人

- 无心人对着有心人

- 无心人说话,只怕有心人来听

- 无心出岫

- 无心吓着有心人

- 无心插柳柳成荫

- 无心炙

- 无心肝

- 无心草

- 无忌

- 无忌审鹞

- 无忓

- 无志之人常立志

- 无志之人常立志,有志之人立常志

- 无志之人常立志,有志之人立长志

- 无志无识,永为人奴

- 无志气

- 无忘耕垄时

- 无忧

- 无忧卡

- 无忧患意识

- 无忧扇

- 无忧无虑

- 无忧无虑,平安无事