张晶晶

摘 要:本文提出当输入中频频率可变时,通过改变AD采样率,使之与中频频率相适应。即将DDC与DDS相结合的实现方法。详述了中频信号频率从60MHz到80MHz,码元速率为1.338M/s时的具体DDC实现方法。最后,通过Simulink对数字下变频的性能进行了仿真,并且在QuartusⅡ下用测试电路实测了数字下变频的性能。

关键词:数字下变频; FPGA; 半带滤波器

中图分类号:TN911.6? ? ? ? ? ?文獻标识码:A? ? ? ?文章编号:1006-3315(2019)8-198-001

一、数字下变频的工作原理及关键技术

数字下变频器的组成与模拟下变频类似,包括数字混频器、数字控制振荡器(Numerically Controlled Oscillator-NCO)和低通滤波器(LPF)三部分。从频谱上看,数字下变频将输入信号从中频变换到基带。这样的处理由两步完成:量化后的中频数字信号进入数字下变频器后,先与数字控制振器NCO (Numerically Controlled Oscillator)产生的本地数字信号混频,然后经过低通滤波,信号变为基带信号。

数字控制振荡器在DDC中相对来说是比较复杂的,也是决定DDC性能的最主要因素之一。NCO的目标是产生一个频率可变的正弦波样本。DDC工作时,每向DDC输入一个待下变频的信号采样样本,NCO就增加一个相位增量,然后按照相位累加角作为地址,检查该地址上的数据,并输出到数字混频器,与信号样本相乘,乘积样本在经低通滤波器后输出,这样就完成了数字下变频。

二、数字下变频的实现

1.在MATLAB下仿真数字下变频

(1)仿真模块的具体结构

在MATLAB下运用Simulink仿真工具对数字下变频进行了仿真,DDC的顶层结构Subsystem1和Subsystem2两部分组成。其中,Subsystem1为数字序列生成模块,产生数字下变频模块中频信号。本文所设计的数字下变频模块可应用到所有中频采样的解调器中。Subsystem2是数字下变频中的核心部分,其中包括混频、滤波两部分。在Subsystem2模块中先由数字控制振荡器产生一个频率可变的正弦波样本。

DDC工作时,在每向DDC输入一个下变频的信号采样本时,NCO就增加一个相位增量,然后,按照相位累加角度作为地址,检查该地址上的数值,并输出到数字混频器,与信号样本相乘,乘积样本再经过低通滤波器滤波后输出,这就完成了数字下变频。

(2)Simulink的仿真结果

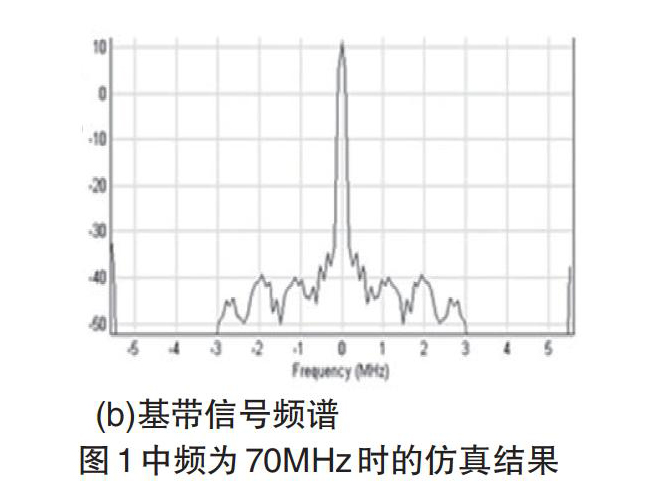

图1给出了输入中频为70MHz时信号在零频附近的频谱图以及下变频后得到的基带信号。

从仿真结果可以看出,当改变中频信号频率时,本文所设计的数字下变频结构可以完成将输入信号从中频搬移到基带的功能。

2.在QuartusⅡ下仿真数字下变频

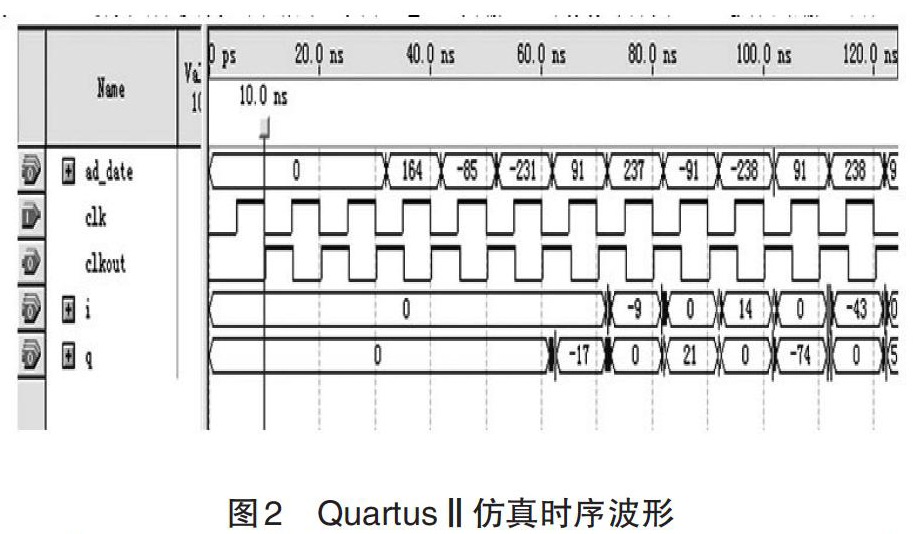

DDC具体用FPGA实现,本文用Verilog语言编写了相应的程序,并用QUARTUSⅡ软件进行仿真。输入中频为70MHZ,码元速率为1.338M/s,采样率为11.2MHz。QuartusⅡ仿真时序波形如下图所示,其中ad_date为输入的中频数字序列,i和q为两路输出结果。

将QuartusⅡ下仿真得到的时序波形结果与MATLAB仿真结果相互吻合。由此验证了本文所提出的当输入中频频率可变时,通过改变AD采样率,使之与中频频率相适应来实现DDC的方法的正确性。这种方案实现简单,节省资源,适用于信号带宽较小时的情况。

参考文献:

[1]宗孔德.多速率信号处理,北京:清华大学出版社,1996

[2]夏宇闻编著.Verilog数字系统设计教程,北京:北京航空航天出版社,2003

- 探析新时期加强国有企业基层党组织建设的思考

- 浅谈思想政治工作在企业行政管理中的重要作用

- 我国事业单位人力资源管理的现状分析

- 关于政府采购降低行政成本的研究

- 法务会计在财务舞弊控制中相关问题研究

- 论股东派生诉讼调解的公司法规制

- 浅谈高校医院规范管理存在的问题与对策

- 浅析新形势下创新型企业青年创新工作难点及对策

- 浅谈国企党建与企业文化建设的共有内涵和共促策略

- 仪控设计组卷

- 基于知识图谱的Altmetrics研究可视化分析

- 浅谈建筑工程施工现场临时用电布置

- 我国现行司法管辖制度改革方案的探讨

- 《德意志意识形态》中的物质生产活动分析及对意识前提的批判

- 浅谈企业工会开展思想政治工作的特点和必要性

- 牡丹江铁路公安处执法规范化研究

- 浅析思想政治教育主客体互动机制的内涵

- 新形势下党工工作的重要性探讨

- 论广东省村居法律顾问制度的普法宣传功能对农村守法意识养成的作用

- 绍兴宣卷传承发展现状及保护意义探究

- 浅论我国古代市舶制度

- 做好新形势下国有企业纪检监察工作的应对措施

- 基层党组织党员服务群众模式的构建探讨

- 全面推进企业纪检监察工作的策略研究

- 中国区域协调发展的演化与展望

- separations

- sept.

- sept

- september

- septembers

- septembral

- septic

- septicaemia

- septically

- septicemia

- septicities

- septicity

- septic tank

- septic tanks

- sepulcher

- sepulchered

- sepulchering

- sepulchers

- sepulchre

- sepulchred

- sepulchres

- sepulchring

- sequel

- sequels

- sequence

- 衣服破损裂缝之处极多

- 衣服破旧

- 衣服破旧的样子

- 衣服破烂

- 衣服破烂不堪

- 衣服破,尚可缝;手足断,安可续

- 衣服等物

- 衣服等非常破烂

- 衣服粗重宽大不合身不合时

- 衣服缝合线外的毛边

- 衣服腋下前后相连的部分

- 衣服腰部的尺寸

- 衣服要从新时惜,孩子要从幼时教

- 衣服要自己穿破,不能叫人从背后指点破

- 衣服轻而凉快

- 衣服边上的镶边

- 衣服长的样子

- 衣服靴帽等的裂缝

- 衣服鞋帽等的总称

- 衣服鞋袜上的补缀处

- 衣服鞋袜等物宽大

- 衣服鞋袜等窄小

- 衣服飘动

- 衣服飘扬的样子

- 衣服首饰