郏宏鑫 郭锐

摘要:为解决3D Flash存储密度增大导致Flash整体误码率不断提高、数据可靠存储时间缩短的问题,提出一种基于循环冗余校验与比特交织的LDPC码3D Flash差错控制方法。该方法首先用CRC判决读取数据是否出错,若出错则实施LDPC纠错,避免浪费纠错资源。在数据读写过程中使用比特交织的方法改变3D TLCFlash逻辑页的比特信息存放顺序,降低3D Flash单一逻辑页误码率过高引起的不必要坏区发生概率。仿真结果表明,在3D TLC Flash信道下,LSB逻辑页的比特误码率下降约35.7%,Flash数据保留时间增加了30.go-/o。该差错控制方法可在3D TLC Flash控制器中实现,不仅可提高3D TLC Flash数据存储可靠性,还可延长3DTLC Flash数据可靠存储时间。

关键词:三维三层单元闪存;低密度奇偶检验码;循环冗余校验;比特交织;差错控制

DOI: 10. 11907/rjdk.191719

开放科学(资源服务)标识码(OSID):

中图分类号:TP393

文献标识码:A

文章编号:1672-7800(2020)004-0247-05

0 引言

3D Flash作为Flash发展的新方向备受关注[1],其存储单元结构复杂,单元间相互干扰比传统平面Flash更严重,因此会产生更多的错误,在3D Flash实际使用过程中,随着Flash擦写次数增加及Flash存储数据时间变长,其可靠性不断下降,因此需改进3D Flash差错控制技术[2-4]。为保证3D Flash存储数据可靠性,目前最常用的方法是采用低密度奇偶检验纠错码进行3D Flash差错控制[5]。张猛等[6]在FPCA平台进行了关于3D Flash错误模式仿真,研究了3D TLC Flash逻辑页误码率特性,将该特性应用到3D TLCFlash LDPC解码过程中,分析优化了解码过程中对数似然信息计算;Cristian等[7]通过机器学习优化LDPC纠错码率,利用3D TLC Flash分析Flash存储耐久性,但是已有研究均未给出具体的3D Flash差错控制应用方案;Nakamura等[8]提出自适应人工神经网络结合LDPC码的纠错方案,通过人工神经网络自适应计算译码信息,可有效纠正错误、延长数据保留时间,但该方法没有考虑到Flash在实际使用过程中数据存储出错比例较小,读取的数据全部參与神经网络迭代译码对数似然信息分析,硬件复杂度高,且仅限于计算机辅助运算,迭代计算量巨大[9-10]。此外即使读取的存储数据存在错误,对错误数据所在页直接进行LDPC迭代译码,也容易出现迭代译码次数过多或迭代译码失败的情况[11-12];Tokutomi[13]针对3D TLC Flash提出一种错误位置记录表的差错控制方法,该方法将Flash错误位置记录到表中,在下一个读取周期中参考错误位置记录表,提前消除部分错误数据,减少重复位置错误,但该方法没有考虑3D TLC Flash逻辑页误码率特性,只是单纯地将存储错误位置记到一个位置更新表中,随着读写次数和数据保留时间的不断增加,表占用存储器容量过高且大容量数据对比计算量巨大,查找操作将显著增加译码时延。

以上方法均未能在兼顾3D TLC Flash逻辑页误码率特性的情况下给出一种低计算复杂度且便于实际使用的3D Flash差错控制方法。因此本文通过分析3D TLC Flash逻辑页误码率特性与Flash纠错过程中不必要的纠错迭代过程,提出提高3D TLC Flash数据可靠存储时长且便于实际使用的差错控制方法。针对3D TLC Flash实际数据存储出错比例较小情况,引入CRC校验码过滤时不需要进行纠错的Flash逻辑页,改进文献[7-8]中不必要的LDPC码纠错迭代计算过程引入的复杂度,同时考虑到文献[6]中3D TLC Flash逻辑页误码率特性,引入比特交织方法改变3D TLC Flash逻辑页中错误信息比特分布情况,将LSB页中较高的误比特率分配至误比特率较低的其余逻辑页中,在总平均误码率不变的情况下,改善3D TLC Flash单一逻辑页误码率过高引起坏区增多的情况,最终构建一种能够提高3D TLC Flash存储可靠性、增加数据可靠存储时长且易于实现的差错控制方法。

1 3D TLC Flash逻辑页错误特征

Wu等[6]对3D TLC Flash存储单元逻辑页误码率进行了FPCA仿真研究,图1和图2显示了在读写次数分别约为3K和6K时,LSB页、CSB页、MSB页误码率与数据保留时长之间的关系[14]。由图1、图2可知,在数据保留时间相同的情况下,随着读写次数的增加,LSB页误码率增幅远大于CSB页和MSB页误码率,CSB页误码率增幅略大于MSB页面误码率。当读写次数一定时,随着数据保留时长的增长,LSB页误码率水平远大于CSB页和MSB页误码率,CSB页误码率略大于MSB页面误码率,并且随着数据保留时间的持续增加,LSB页误码率情况始终较高。

在3D TLC Flash数据存储过程中,当存储单元所在MSB、CSB、LSB页的其中一个逻辑页误码率过高且超过LDPC差错控制器纠错能力阈值时,该逻辑页会由于误码率过高而纠错失败,此时即使位于该逻辑页字线的其它逻辑页能够通过LDPC差错控制器成功完成纠错,这些逻辑页所在存储区仍旧会被Flash控制器判定为坏区[14],该现象严重影响了3D TLC Flash长时间数据存储可靠性。由于3D TLC Flash中不同逻辑页能够正确存储数据的能力不同,其中MSB页能够正确存储数据的时间最长,CSB页次之,LSB页最差。因而LSB页误码率情况是影响3DTLC Flash长时间数据存储的关键因素。随着3D TLCFlash存储时间的延长,如果LSB页误码率性能恶化到超过LDPC差错控制器的纠错阈值,则即使在MSB页,CSB页误码率在可被正确译码还原数据的情况下,该逻辑页所在区也会被Flash控制器认作为坏区进行处理,从而影响存储性能。图3描述了3D TLC Flash逻辑页误码率与LD-PC纠错能力的关系,随着Flash使用时间的延长,所有逻辑页误码率均不断增加,当某一逻辑页误码率达到Flash纠错码最大纠错阈值时,该逻辑页所在区域将不可靠。因此为提高3D TLC Flash长时间正确存储数据的能力,需解决LSB逻辑页误码率问题,使LSB页误码率曲线在达到LDPC码纠错能力阈值时,对应的数据保留时间尽量长[15]。

2 3D TLC Flash差错控制方法设计

3D TLC Flash改善纠错性能需要考虑两个问题:①Flash纠错效率问题,即如何提高数据处理有效性;②Flash逻辑页经过大量擦写后,随着数据保留时间的延长,LSB页误码率突兀、纠错性能差的问题,即如何提高数据存储可靠性。

针对问题一,本文引入CRC码,检查读取数据是否出错。CRC码作为检错码需在校验开始前选择一个能代表特定二进制数字的多项式。在消息发送和接收时均需用到多项式,且它的MSB位和LSB位都是1;其次将需要发送的消息先与该多项式进行数模2除运算,得到传输需要的CRC码并把它添加到发送消息的末尾,再经过信道进行传输[16]。生成的新序列能让发送端和接收端共同选定的某个特征进行数模2运算,如果有余数,则说明数据帧在传输过程中出错;如果运算后为0,则说明数据在传输过程中没有发生错误[17-18]。由于Flash页中存在错误的比特数占全部数据比特的比例很小,引入CRC码可以让本来不存在错误的Flash页避免计算量复杂的LDPC纠错译码运算,从而提高Flash纠错效率与数据处理有效性[19]。

针对问题二,本文在Flash纠错控制器中引入比特交织器。Flash中的错误会使存储单元状态发生转变,其中单元存储状态转移到相邻状态较为容易,而跨越相邻状态转变成其它次级状态则十分困难。另外,Flash中的错误会使存储单元从含有较少电子的存储单元状态向具有较多电子数量的存储单元状态转移[20]。结合图4的存储单元状态分析可知,3D TLC Flash的单元状态转变绝大部分是相邻状态间的转变,并且转变呈现L0→L1→…→L7这样电平值增大的趋势[6]。

传统TLC Flash存储二进制信息比特可由图5表示(彩图扫描OSID码可见,下文同),可以看到数据是按照TLC存储单元最高位有效位、中央有效位、最低有效位的形式,分别拆分、并行存人对应字线的MSB、CSB、LSB页3个逻辑页中去,其中信息比特中加粗的是数据存入TLCFlash逻辑页中一定时间内,发生错误的位置对应TLCFlash逻辑页的红色二进制比特。由于TLC Flash在长时间数据保留过程中,LSB逻辑页误码率最高,如图5中的信息比特流存储于逻辑页错误分布情况描述,由于LSB位比特誤码率高,所以存储到逻辑页中后LSB页的比特误码率明显高于CSB页和MSB页,此外CSB页的比特误码率略高于MSB页。数据未出错存储情况下的位线状态也在图5中给出,以便与逻辑页数据比较。其中信息比特序列出错情况是最低有效位容易发生错误,而中央有效位和最高有效位出错概率较小。

经过比特交织处理后的TLC Flash存储二进制信息的比特方式如图6所示,可以看到数据在存入逻辑页前首先对数据段进行了均匀分段,分段后的数据分别依次串行输入到MSB、CSB、LSB逻辑页中,而不同于传统方法中的最高有效位只存储在MSB逻辑页、中央有效位只存储在CSB逻辑页、最低有效位只存储在LSB逻辑页的存储数据形式。其中加粗的信息比特与Flash逻辑页中红色二进制比特如图5所述。数据未出错存储情况下的位线状态同样也已给出。对比图5所示的传统TLC Flash逻辑页的存储方式,TLC Flash长时间存储信息条件下,两种方案的Flash逻辑页平均误比特率相同,但经过比特交织处理后的存储形式LSB页误比特率得到了明显改善,传统方案LSB页的比特误码率在图5中约为0.625,而串并转换方案LSB页的比特误码率在图6中约为0.375。虽然MSB页和CSB页的误比特率有一定程度的增加,但随着信息比特长度的增加,它们的误比特率远低于传统LSB页的误比特率,只要LSB页的误比特率在逻辑页可被LDPC码正确纠错的阈值之内,则这3个逻辑页均可纠错译码。

通过在数据写入3D TLC Flash逻辑页前进行比特交织处理,改变错误信息比特在Flash逻辑页中的分布情况,将LSB页中存在较高的误比特率分配至误比特率较低的其余逻辑页中,在总平均误码率不变的情况下,略微增加MSB和CSB逻辑页的误比特率,可减少3D TLC Flash中LSB页较大误比特率造成的单一逻辑页误码率过高引起坏区增多的情况,从而大幅提高3D TLC Flash长时间存储数据的可靠性。本文提出的Flash纠错方法添加了通信硬件中常用的CRC校验模块与交织模块,因此可以在3D TLCFlash控制器中实现。

3 3D TLC Flash差错控制方法仿真

3.1 差错控制方法框图

3.1.1 数据写入阶段

将长度为k的用户数据信息X{x1,x2,…,xk)分别经过CRC编码器和LDPC编码器处理,得到长度为r1的CRC校验位(记作CRC-P)和长度为r2的LDPC校验位(记作LDPC-P)。将长度为k的用户信息、长度为r1的CRC校验位信息以及长度为r,的LDPC校验位信息组成总长度为n的码字C{c,,c2,…,ct,Ck+l,Ck+2,…,Ck+1,Ck+rl+l,…,Cn),其中n=k+r1 +r2。将码字C经过比特交织分段处理后,改变原有逻辑页数据存储顺序并写入到TLC Flash存储器中。其中用户信息存储在Flash数据区,CRC校验位和LDPC校验位存储在Flash冗余区。数据写入阶段框架如图7所示。

由图8可知,Flash纠错方法用到2个交织器件与CRC编译码器模块,硬件复杂度略有所增加,但数字电路为常用模块,因此可以在3D TLC Flash控制器中用逻辑电路实现。

3.2 仿真分析

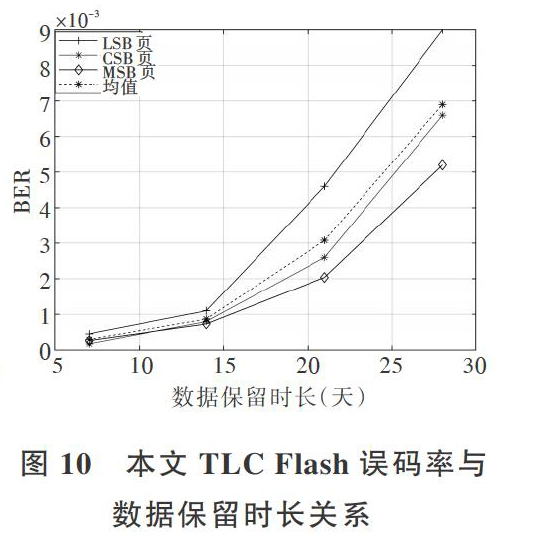

本部分对基于CRC和比特交织的LDPC码的3DFlash差错控制方法进行仿真,仿真信道为3D TLC Flash信道(}昆合噪声信道),分别对传统3D TLC差错控制方法与本文提出的差错控制方法进行测试,测试时长为4周,每天对3D TLC Flash循环随机擦写次数约50次,统计擦写完成后相应的Flash逻辑页误码率情况见图9和图10。

可以看到在擦寫测试周期里,传统TLC数据存储方法随着数据保留时间的增加,各个逻辑页的比特误码率均有提高,LSB逻辑页的比特误码率曲线斜率明显高于MSB和CSB逻辑页,且数据保留时间越长,LSB逻辑页与MSB、CSB逻辑页之间的比特误码率差距越大。本文提出的基于CRC与比特交织的LDPC码3D Flash差错控制方法随着数据保留时间的增加,各个逻辑页比特误码率均有提高,且CSB、MSB的比特误码率增幅比传统方法更大。但是LSB逻辑页的比特误码率有明显改善,在测试周期结束后测得LSB页比特误码率由0.014降低到了0.009,下降幅度约为35.7%。两方案的平均逻辑页误码率相近,说明本文方法降低了3D TLC Flash LSB页单一逻辑页误码率,提高了3D TLC Flash长时间存储数据的可靠性。

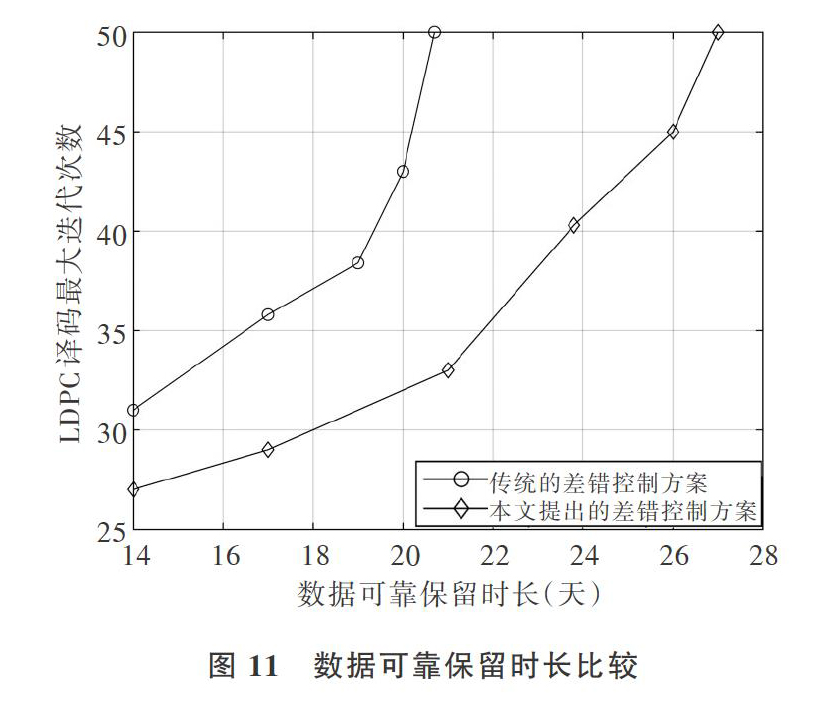

调节LDPC差错控制器设定的最大迭代次数可以改变系统纠错能力,从而得到LDPC译码迭代次数与Flash数据可靠保留时长之间的关系(见图11),可以看到在擦写测试周期里,当LDPC最大迭代次数为50时,传统TLC数据存储方法的可靠数据保留时长约为20.7天,而本文提出的基于CRC与比特交织的LDPC码3D Flash差错控制方法数据可靠保留时长约为27.1天,数据可靠保留时间增加了30.9%,且在相同数据可靠保留时长的条件下,本文提出差错控制方法所需最大迭代次数比传统3D TLC数据存储方法更少,这表明本文方法加快了纠错迭代速率,从而具有较好的译码性能。

4 结语

本文提出了一种基于CRC与比特交织的LDPC码3DFlash差错控制方法。针对Flash实际数据存储出错比例较小情况,引入CRC校验码过滤不需要进行纠错的Flash逻辑页,提高TLC Flash纠错效率;针对Flash逻辑页中LSB页存在较高误比特率的问题,引入比特交织方法改变错误信息比特在Flash逻辑页中的分布情况,将LSB页存在的较高误比特率分配至误比特率较低的其余逻辑页中,在总平均误码率不变的情况下减少3D TLC Flash LSB页中大误比特率造成的单一逻辑页误码率过高引起坏区增多的情况,提高了3D TLC Flash存储可靠性。3D TLC Flash仿真擦写测试结果表明,LSB逻辑页比特误码率下降幅度约为35.7%,Flash数据保留时间增加了30.9%。同时,因本文方法添加了常用的CRC校验模块与交织模块,使该方法可在3D TLC Flash控制器中实现。

参考文献

[1]

KANG D. JEONC W, KIM C, et al. 256 Cb 3 h/cell V-NAND flashmemory with 48 stacked WL layers [J]. IEEE Journal of Solid-StateCircuits, 2017 , 52( 1) : 210-217.

[2]

WONG G. SSD market overview [M]. Inside Solid State Drives (SS-Ds) . Dordrecht: Springer, 2013.

[3]

TANAKAMARU S. YANACIHARA Y. TAKEUCHI K. Highly reli-able solid-state drives ( SSDs) ,vith error-prediction LDPC ( EP-LD-PC ) architecture and error-recovery scheme [ C]. 2013 18th Asia andSouth Pacific Design Automation Conference , 2013 : 83-84.

[4]

TOKUTOMI T, DOI M. HACHIYA S, et al. 7.7 enterprise-grade 6xfast read and Sx highly reliable SSD with TLC NAND-flash memoryfor big-data storage [ C ] . 2015 IEEE International Solid-State CircuitsConference. 2015 : 1-3.

[5]

NAKAMURA T, DEGUCHI Y, TAKEUCHI K. AEP-LDPC ECC witherror dispersion coding for burst error reduction of 2D and 3D NANDflash memories [Cl. 2017 IEEE International Memory Workshop,2017 : 1-4.

[6]

WU F, ZHANC M. DU Y, et al. Using error modes aware LDPC to im-prove decoding performance of 3D TLC NAND flash [J/OL]. IEEETransactions on Computer-Aided Design of Integrated Circuits andSystems :

1,

201 9-02-05.

https : //ieeexplore.ieee.org/document/8634908.

[7]

ZAMBELLI C , CANCELLIERE G . RIGUZZI F . et al. Characterizationof TLC 3D-NAND flash endurance through machine learning for LD-PC code rate optimization[ C ] . 2017 IEEE International Memory Work-shop (IMW) . 2017 : 1-4.

- 新课程改革背景下高中英语教学思考

- 巧用小组合作,优化高中信息技术教学

- 新课标下高中信息科技“分支结构”单元逆向教学设计初探

- 高中信息技术教学中合作学习的有效性分析

- 信息技术核心素养背景下对教师的能力要求探析

- 微课在高中信息技术操作课中的设计与应用初探

- 信息技术在体育教学中的应用

- 探讨微课在高中物理教学中的应用

- 新高考模式下用微课辅助一轮复习教学的实践研究

- 微视频资源在高中物理教学中的应用初探

- 基于微视频的高中数学试卷讲评课的翻转课堂教学分析

- 基于智慧课堂模式下的高中数学教学

- 智慧课堂对高中数学试卷讲评课有效性的启示

- 基于云平台的高三化学反应原理微课资源库在复习中的应用

- 例谈信息技术背景下高中哲学一轮复习

- 数字校园教育信息化环境建设及其在高中历史教学中的应用研究

- 有关在高中英语教学中高效使用TED资源的思考

- 微课在高中英语教学中的应用及启示

- 论网络流行语对高中语文教学的影响及所采取的对策

- 高三英语复习的技巧与策略

- 手机对初中生学习的负面影响及对策

- 家庭教育莫轻看 转变观念先育德

- 浅谈中考语文复习的有效性

- 浅谈中国画的继承与发展

- 以“真实”的名义教书育人

- musters

- muster-up

- mustest

- musthave

- must-have

- musths

- mustier

- musties

- musties'

- mustiest

- mustily

- mustiness

- mustiness'

- mustinesses

- mustiness's

- musting

- must not

- must not/mustn't

- mustn't

- musts

- musty

- musty's

- must²

- must¹

- mutant

- 青苍青旷

- 青苔

- 青苔巷

- 青苔赋

- 青苗

- 青苗法

- 青苗簿

- 青苗钱

- 青苹

- 青苹风

- 青茁

- 青茶

- 青茸茸

- 青荃射干

- 青草

- 青草只是一夏之盛,苍松可是四季常青

- 青草地

- 青草地里放老驴——个个饱

- 青草没马蹄,拜年也不迟

- 青草浓茂的样子

- 青草盖牛蹄,正是拜年时

- 青草送进牛嘴里——扯不清

- 青草黄茅瘴,不死成和尚

- 青草黄茅瘴, 不死成和尚。

- 青荷