李浩 戴志涛

摘要:随着信息社会的迅猛发展,传统的单核处理器及同构多核已难以满足大数据处理的高性能需求,采用ARM和FPGA构建异构多核系统,以FPGA上的IP核作为硬件加速器,ARM提供通用计算成了高性能计算领域的重要发展趋势。本文针对当前应用最广泛的H.264视频编码算法,构建了ARM-FPGA异构多核系统,提出了基于共享内存和AXI总线的高带宽通信方法。将编码算法中耗时较多的模块负载到FPGA上运行,利用FPGA丰富的逻辑资源和并行性加速编码,移植嵌入式Linux到ARM上并开发相关驱动,实验数据表明H.264编码算法在ARM-FPGA异构多核系统中效果较好,编码速度明显加快,且有很好的扩展性和灵活性。

关键词:视频编码;异构多核;FPGA;H.264

中图分类号:TP37

文献标识码:A

0 引言

随着科学技术的创新,云计算和移动互联网的迅猛发展使得各领域对海量数据的处理能力要求越来越迫切。传统的单核处理器已满足不了当下的计算要求,为此,人们提出了多核处理器解决方案。多核处理器共有两种架构,同构多核架构(Homogeneous MPSoc)和异构多核架构(Heterogeneous)。同构多核系统由功能相近的处理器构成,如Intel系列,ARM Cortex-A9系列。异构多核系统是由功能相异的处理器构成,如IBM的Cell处理器,AMD的APU等。H.264是由ISO/IEC与ITUT合作成立的联合视频专家组(JVT:Joint Video Team)于2003年制定的视频编解码标准,其主要包括视频编码层(VCL:Video Coding Layer)和网络适应层(NAL:Network Adaptation Layer)。

纪芳提出了一种基于FPGA同构多核处理器的AVS视频编码算法实现方案,使用Xilinx官方提供的MicroBlaze软核构建同构多核系统,其中一个软核作为主核,负责线程调度任务和任务分配,剩余的软核作为协处理器负责执行具体某些编码算法模块。优点是充分利用了FPGA逻辑资源丰富的特点,适合运行并行算法,缺点是系统的流程控制和数据运算都由FPGA实现,硬件描述语言开发难度大。

江辉提出了一种基于CPU-GPU的异构多核架构的H.264编码算法实现方案,在该架构中GPU作为CPU的协处理器,CPU串行执行任务,而GPU并行执行CPU分配的任务。CPU和GPU各自有自己的专用的存储器以及数据访问通路,因此相较于同构多核处理器有更大的存储器带宽和计算性能,缺点是GPU开发使用的CUDA是设备相关的,可扩展性较差。

本文在前人研究基础上,结合Zynq开发板单芯片集成了双核ARM和FPGA的特点,提出了一种基于ARM-FPGA的异构多核高性能架构,设计了一种异构多核间高带宽通信方式,移植了嵌入式Linux并开发相关软核的驱动,在该架构实现了优化后的H.264编码算法,实验数据表明,该架构下的算法相比同构多核架构具有很大性能的提升。

1 基于Zynq的异构多核系统总体设计

1.1异构多核系统的硬件架构设计

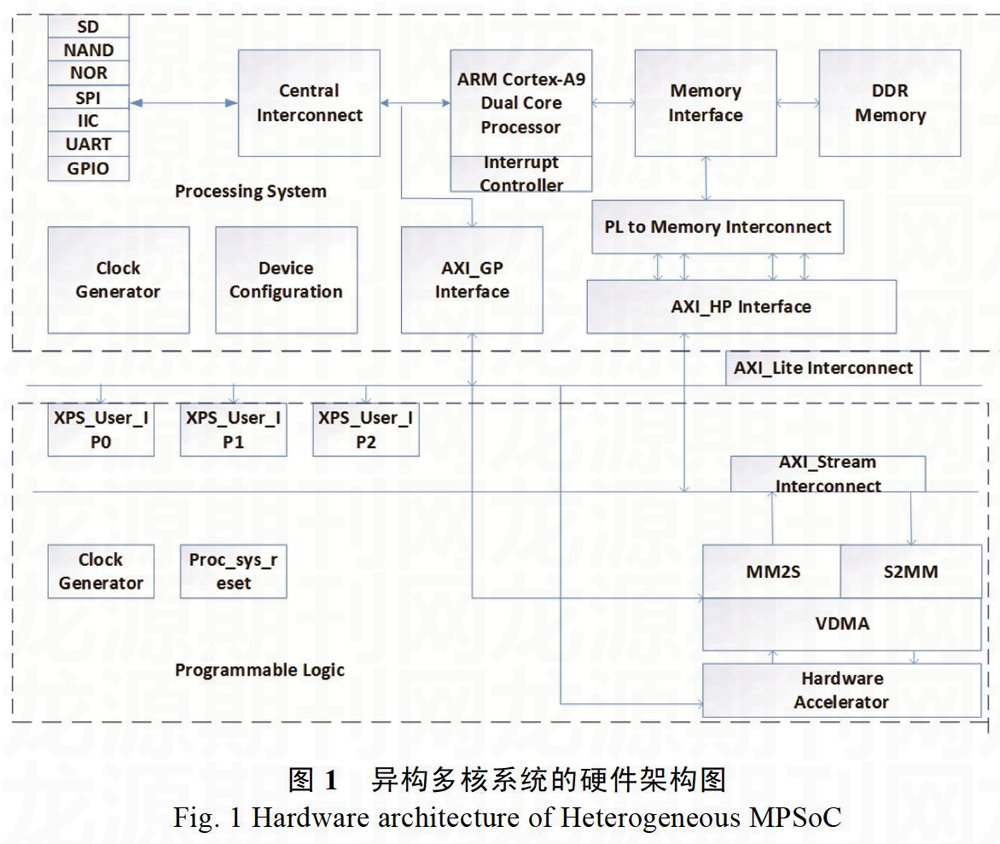

本文使用的硬件平台是Xilinx Zynq-7000 SOC,在单芯片集成了具有丰富特点的双核ARM Cortex-A9处理器的处理系统和Xilinx可编程逻辑,整个异构多核系统的硬件架构设计如图1所示。

处理系统不仅包括ARM Cortex-A9双核处理器,还包括Cache,DDR控制器,DMA控制器等。可编程逻辑采用Xilinx 7系列的FPGA技术,它包含大量不同类型的资源,主要包括块存储器(Block RAM),时钟管理单元(Clock Management Tiles),可配置逻辑块(Configurable Logic Block)等。ARM Cortex-A9双核处理器和Xilinx7系列FPGA集成到单芯片中构成了本文所介绍的异构多核处理器系统。由于Zynq既有通用处理器的灵活性和可扩展性,又有具有可编程逻辑处理器的高性能,可重构性,因此本文在此硬件平台上构建了异构多核的处理器系统,完成了H.264编码算法在异构多核系统上的优化实现。

1.2异构多核系统的软件架构设计

为了在异构多核系统上运行H.264编码算法,本文将嵌入式Linux系统移植到Zynq开发板,并开发相关驱动。在Zynq异构多核硬件系统上移植Linux系统的步骤如图2所示。

在异构多核硬件系统搭建完毕及嵌入式Linux移植完成后,本文将在软件层实现H.264编码算法。

如图3所示,运行过程中以下文详述的ARM-FPGA高速通信方法及FPGA硬件加速算法的调用为基础,将编码算法中耗时最多的任务负载到FPGA中去执行,编码算法运行时其他阶段仍在ARM中执行。ARM将待处理数据通过AXI HP高速通信接口传递给FPGA,FPGA运算完成后同样通过AXI HP接口返回给ARM。

2 异构多核系统间通信方法的设计与实现

Zynq由于将不同工艺的异构多核融合在一个芯片,如何保证Cortex-A9和FPGA之间的互联数据通路高速稳定,是基于Zynq芯片设计的重点。Zynq中异构核间的通信接口共有9个,主要如下类型:

AXI ACP接口:ARM多核架构下定义的一种接口,加速器一致性端口用来处理DMA之类不带缓存的AXI外设,Ps端是Slave接口。

AXI HP接口:高性能,高带宽的AX13.0标准的接口,共有4个,PL模块作为主设备连接。

AXI GP接口:通用AXI接口,共有4个,主要用于对外设端口进行配置,是低速端口。

异构多核通信的主要思想是共享内存,因此本文主要设计了基于AXI GP接口的低速通信方法和基于AXI HP接口的高速通信方法,确保PL和PS数据交互通路高效传输。

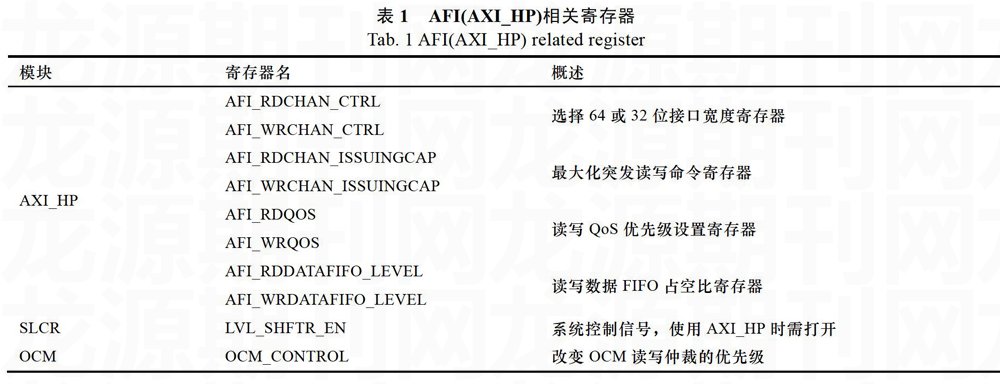

AXI HP的功能和表1中的寄存器相关,本文设计并实现了高速通道接口在Linux下的驱动程序,主要是通过这些寄存器来配置AXI HP接口。

2.1异构多核系统的软件架构设计

Zynq平台一共提供了四个AXI HP接口,每个接口都有两个FIFO缓冲器,一个是读缓冲,一个是写缓冲。由于AXI_HP接口用于高速通信,因此使用AXI3.0通信协议,ARM核可直接接访问DDR内存,而FPGA通过AXI_HP接口访问DDR内存和片上存储器OCM,异构多核通过AXI_HP接口使用共享内存的方式进行通信,具体的数据传输方式是通过DMA实现的。AXI_HP接口是为了PL访问PS上的存储器(DDR和On-Chip RAM)而专门设计的高速数据通路,因此它支持标准的AXI_3.0接口,可以跨PS和PL的AXI接口之间的异步时钟域,可编程的32位/64位数据宽度。AXI_HP端口分成两部分,一部分和PL直接连接,另一部分连接到AXI_Interconnect,从而访问DDR和OCM。

AXI_HP端口用于PS和PL部分的高速数据交互,其数据搬移一般通过逻辑内的DMA控制器而不需要CPU参与,因此本文用异构多核处理器运行H.264编码算法时数据的传输便是通过AXI_HP接口传输到DDR中,供CPU和FPGA完成进一步的图像处理。

2.2异构多核系统的软件架构设计

Zynq平台一共提供了4个AXI_GP接口,两个主接口以及两个从接口,基于AXI_GP接口的低速通信流程如图4所示。异构核间ARM核作为主设备,FPGA作为从设备,ARM核与FPGA核间通信主要通过ARM核对从设备的端口寄存器读写来实现。本文设计并实现了FPGA中的自定义IP核在Linux下的驱动程序,具体实现了AXI_IP_OPEN,AXI_IP_CLOSE,AXI_IP_READ,AXI_IP_WRITE,AXI_IP_IOCTL等函数,命名及实现方式均符合Linux标准的驱动程序实现规范。

3 异构多核系统上H.264编码算法的实现

3.1H.264视频编码算法

目前主流的H.264视频编码标准有三种:JM参考模型,T264,X264。JM参考模型是ITUT组织的一个官方的编码参考程序,一般用于开发者学习和比对使用,功能完善但编码效率低。T264是中国开源爱好者组织开发的H.264视频编码程序,由于与其他解码器兼容性不好,目前已停止更新。X.264是法国人组织开发的H.264视频编码算法,目前仍有开源社区维护该项目。它的兼容性好且编码效率高,因此本文选用X264算法作为异构多核系统上编码算法的基础。此外,对于视频编码的核心模块,如帧内预测、变换量化等模块,需要大量运算的模块针对不同的处理器做了相适应的指令集优化,利用相关的多媒体扩展指令集来改善编码性能。我们以x264算法为原型,通过在PC机平台上的实际测试,同时结合一些前人的工作成果,来分析总结H.264标准视频编码器在编码过程中耗时过多的模块,并根据分析结果确定相应的软硬件划分方案。x264_clip_uint8是x264算法耗时最多的函数,其次是hpel_filter、_abs、x264_pixel_sad_16x16、quant_4x4函数。hpel_filter函数中耗时最多的部分也为x264_clip_uint8;而abs是预测编码中计算子块的计算用于模式选择依据的子块绝对差和所必须要的函数,而x264_pixel_sad_16x16则是计算16x16块的绝对差和的函数。

3.2测试结果与分析

本文在Zynq7000开发板上实现了x264编码器算法,编码测试了三个视频序列分别为Bus,City,Football(CIF352x288),编译环境是Linux下的Gcc,测试帧数为100帧。通过对比ARM-FPGA异构多核架构和ARM同构多核架构的同一帧YUV图像统计信息,如表2所示,两者编码后图像质量上基本一致,但编码时减少了30%左右。这表明本文提出的方法是有效的,相较ARM同构多核时编码性能有大幅的提升。

4 结论

本文针对Zynq开发板单芯片集成双核ARM和FPGA的特点,提出了一种基于ARM-FPGA的异构多核硬件架构,设计了一种异构多核间高带宽通信方式,移植Linux并开发相关驱动,在该架构实现了优化后的H.264编码算法。通过对视频序列编码在ARM同构多核环境下进行比对,硬件加速效果明显。目前最新的编码标准是HEVC,其特点是复杂度高,压缩比大,理论上适合运行在本文介绍的异构多核系统上,下一步的研究方向可致力与此。

- 神秘探寻之旅细数苗族二三事

- 苗王城 苗疆上的军事领地之秘

- 苗疆 苗王城 苗王

- 试论温庭筠词的艺术特色

- 论唐宋词对当代流行歌曲的渗透和影响

- 浅析布列松摄影思想

- 浅谈古斯塔夫?马勒交响乐的研究理路

- 鸟崇拜与民族审美文化

- 人类学纪录片《最后的山神》的人类学思想

- 古代女性文学形象对当代的启示

- 青花绽放,一抹“瓷”光

- 探访故宫里的“文物医院”

- 从灵岩寺罗汉看宋代彩塑的艺术特点

- 地震监测方法现状研究

- 关于碎裂钻井技术极其在地热钻井中的应用前景分析

- 地下水对深基坑支护工程的影响及险情处理

- 混合土的工程勘察及其地基承载力的确定方法分析

- 关于地质找矿的遥感技术运用解析

- 广西区体工二大队山体滑坡治理工程的方案比选

- 高密度电法在水文地质和工程地质中的应用

- 物探方法在隧道勘查中的运用

- 浅析地质工程找矿中的大比例找矿技术

- 大同城市地域结构分析

- 山区公路桥涵设计的一般性原则探讨

- 地理环境对人们语言发展的影响

- recomparisons

- recompensable

- re-compensate

- recompensate

- recompensated

- recompensates

- recompensating

- recompense

- recompensed

- recompenser

- recompensers

- recompenses

- recompensing

- recompensive

- recompilations

- recompilation's

- recompiled

- recompiles

- recompiling

- recomplete

- recomplicate

- recomplicated

- recomplicates

- recomplicating

- recomplication

- 毒酒

- 毒闷

- 毒阱

- 毒雾

- 毒雾愁云

- 毒饵

- 毒骂

- 毒魔狠怪

- 毒鳞

- 毒龙

- 毒(独)门儿

- 毓

- 毓养

- 毓德

- 毓秀钟灵

- 毓精

- 比

- 比一定的时间靠前

- 比一定的时间靠后

- 比上不足

- 比上不足,比下有余

- 比下有余

- 比不上

- 比不得

- 比世