范毅 李明华

【摘要】 ? ?本文介绍了一种基于FPGA的PCI接口ARINC429适配器的设计、实现,采用PLX提供的基础驱动封装了功能函数库,并在Labview下进行了测试。

【关键字】 ? ?ARINC429 ? ?PCI ? ?FPGA ? ?PLX ? ?Labview

Design and implementation of PCI interface ARINC429 adapter based on FPGA

FAN Yi,LI Ming Hua

(Xian Institute of Aeronautical Computing Technology for Aeronautical Industry,Xian Shannxi 710068 China)

Abstract:This paper introduces the design and implementation of a PCI interface ARINC429 adapter based on FPGA,Functional libraries are encapsulated using the underlying drivers provided by PLX and tested under Labview.

Keywords:ARINC429、PCI、FPGA、PLX、Labview

一、概述

为实现ARINC429总线的自动测试,需要具有大数据量连续发送和自动接收能力的模块,且该模块应便于与测试上位系统连接。

模块实现8路ARINC-429信号的接收和4路ARINC-429信号的发送。同时为每路ARINC-429信号提供1K帧(1帧32byte)的循环缓冲区。

二、总体思路

考虑实现的便捷和可靠,ARINC429部分采用标准协议芯片实现,采用标准协议芯片实现可避免因数据编码等原因影响测试可靠性,缩短开发和调试周期;与上位机采用PCI接口连接,接口使用专用桥接芯片;内部数据流控制采用FPGA实现。

2.1 ARINC429总线

ARINC429总线协议是美国航空电子工程委员会(Airlines Engineering Committee)于1977年7月提出的,并于同年同月发表并获得批准使用。它的全称是数字式 信息传输系统DITS。协议标准规定了航空电子设备及有关系统间的数字信息传输要求。ARINC429广泛应用在先进的民航客机以及俄制军用飞机中。我国与之对应的标准是HB6096-SZ-01。

ARINC429总线结构简单、性能稳定,抗干扰性强。最大的优势在于可靠性高,这是由于非集中控制、传输可靠、错误隔离性好。

2.2 ?PCI总线

PCI是Peripheral Component Interconnect(外设部件互连标准)的缩写,使用较为广泛。PCI总线是一种同步的独立于处理器的32位或64位局部总线,最高工作频率为33MHz,峰值速度在32位时为132MB/s,64位时为264MB/s,总线规范由PCISIG发布。ISA总线相比,PCI总线具有高速、支持即插即用、可靠性较高、扩展性较好等显著的优点,但也存在规范严格、使用复杂等缺点,因此在实际设计和开发过程中,一般使用专用芯片实现从PCI总线到Local Bus的转换,从而简化开发工作,也可使用对应的IP核,进一步缩减期间数量,提高集成度,目前主流FPGA厂商都提供了免费的PCI桥IP核。

2.3 FPGA

FPGA(Field Programmable Gate Array)是在PAL、GAL等可编程器件的基础上进一步发展的产物。FPGA在复杂时序逻辑的实现上具有先天的优势,同时具备硬件电路并行运行的特点。

三、系统结构及模块功能设计

3.1系统结构

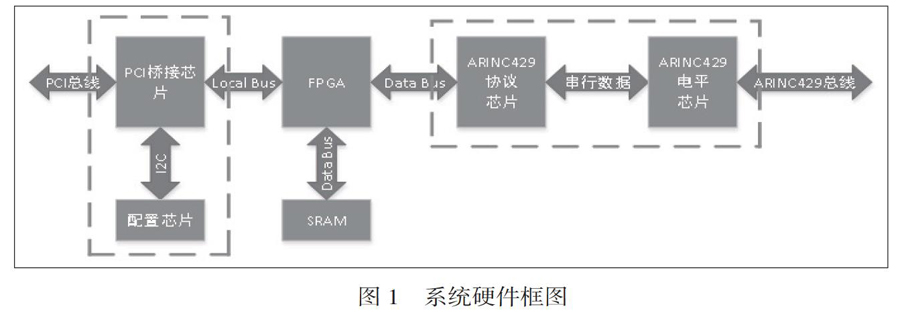

系统硬件框图如图1所示,由3个模块组成,分别为PCI接口(包括PCI桥接芯片和配置芯片)、FPGA、SRAM、ARINC429接口(包括ARINC429协议芯片和ARINC429电平芯片)。

PCI接口接收上位发来的配置和控制数据,并传递给FPGA内的控制逻辑;FPGA内的逻辑根据配置和控制数据进行ARINC429协议芯片的初始化,并对接收和发送缓冲区进行初始化;需要发送数据时,上位将需要发送的数據写入发送缓冲,并通过控制寄存器启动发送,通过读取发送状寄存器了解发送情况,通过控制寄存器可实现循环和单个数据重复发送;接收在完成配置后根据ARINC429协议芯片的接收中断自动进行,并按照先后顺序存储在接收缓冲区,模块不产生中断,上位机可读取接收状态寄存器了解接收情况,逻辑采用VerilogHDL设计实现[1]。

本设计中,PCI桥接芯片选择Broadcom(原PLX)公司的PCI9052,该芯片为PCI从设备接口桥芯片,可方便的将PCI转化为ISA(Local Bus),PCI总线符合PCI 规范r2.1;FPGA使用Xilinx公司Spartan6系列的XC6SLX25(FT);ARINC429的协议芯片时使用4片HoltIC公司的HI3282,每片HI3282集成1路发送和2路接收,自带接收电平转换,发送电平转换芯片使用HI-8585。

3.2 FPGA内功能划分

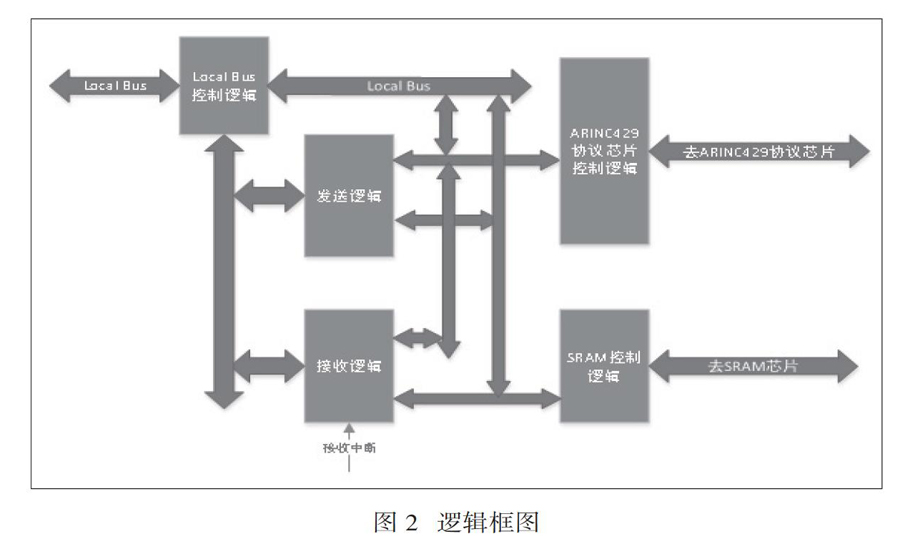

如图2所示,FPGA内逻辑分为Local Bus控制逻辑、接收逻辑、发送逻辑、ARINC429协议芯片控制逻辑和SRAM控制逻辑。

3.2.1 Local Bus控制邏辑

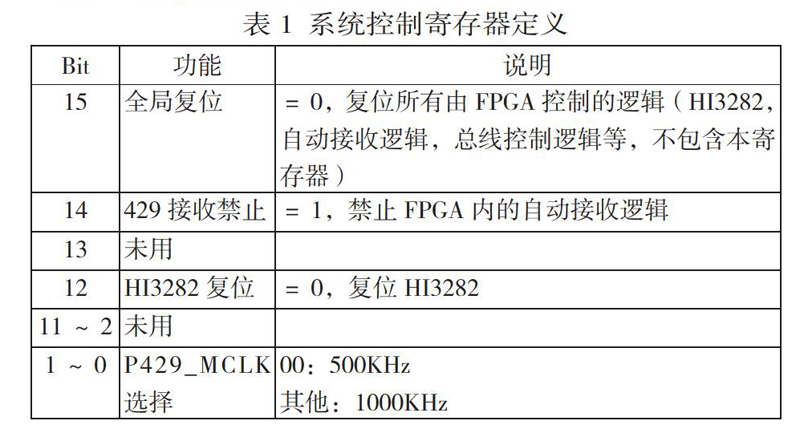

Local Bus控制逻辑内包含Local Bus信号的译码和系统控制和状态寄存器,译码用于选定内部逻辑功能,系统控制和状态寄存器定义如表1和表2。

3.2.2发送逻辑

发送逻辑根据发送控制寄存器启动发送,并将发送相关的状态(主要是ARINC429协议芯片接收相关输出)保存扫发送状态寄存器。启动发送后,根据发送缓冲区地址和状态寄存器内相关位,自动完成从SRAM读取数据、写入HI-3282发送缓冲、等待发送完成、再次取数(地址指针可通过寄存器获得)的循环,直至完成缓冲区内所有数据发送。

上位机在发送前首先需要完成ARINC429协议芯片的初始化,初始化由Local Bus控制逻辑直接操作ARINC429协议芯片完成。完成初始化后,设定发送缓冲区起始地址及大小(通过寄存器),随后将数据写入缓冲区对应地址(完成缓冲区起始地址及大小设置后,设置立即生效),通过设置发送控制寄存器启动发送。涉及的寄存器见下表。

3.2.3 接收逻辑

接收逻辑监控4片HI3282上8个通道的Drin信号,当该信号有效时,启动自动接收逻辑,将ARINC429协议芯片内的数据转存至SRAM。

在使用自动接收逻辑前,需配置接收缓冲区起始地址及大小。

3.2.4 SRAM控制逻辑

SRAM控制逻辑完成访问仲裁和SRAM控制。Local Bus控制逻辑、接收逻辑、发送逻辑均可访问SRAM,优先级从高到低为:接收逻辑、发送逻辑、Local Bus控制逻辑,当高优先级逻辑访问时,低优先级的访问将被忽略,因此在进行操作前应确认模块工作状态,以免出现无效操作。

3.3 PCI总线接口

PCI9052可通过串行EEPROM配置,也可由上位机进行配置。

本设计中结合两种方式,EEPROM用于模块识别,上位机对Local Bus相关寄存器进行配置,以方便软件编程和调试。

3.4 ARINC429总线接口

由4片HI3282和4片HI8585组成,ARINC429协议芯片完全由FPGA控制,包括基础时钟及复位信号。

四、驱动开发与模块测试

4.1 驱动软件

PCI9052提供配套的软件驱动包(内含调试工具PLXmon),在进行快速测试和驱动软件开发时,可使用该工具包进行[2]。PLXmon软件界面见下图3。

软件开发包提供标准PCI函数库(针对不同类型的桥片有不同函数),通过调用标准函数可快速实现功能。下表6是用于操作模块的专用函数[3]。

4.2 系统测试

测试分为两步,首先进行自回绕测试,自发自收以验证功能;随后与目标被测件进行连接,进行连续接收测试(测试中只需接收)。为方便测试,使用Labview编制测试用软件,监控测试并记录数据[4]。软件界面如下图。

测试项及结果如下表7。

五、结束语

本文基于FPGA设计了可自动大量缓存接收数据的PCI接口ARINC429总线适配器。经过长时间测试,模块工作稳定,自动接收功能可大量缓存接收数据,为自动测试ARINC429 总线提供了便利。

参考文献

[1] [美]Samir Palnitkar,Verilog HDL数字设计与综合(第二版),电子工业出版社,2004.

[2] 丁高磊、王新艳,PLX9052的配置及驱动开发,计算机与信息技术,2007(22),51-52.

[3] 熊松,基于PCI总线的数据采集卡的实现,东南大学,硕士学位论文,20020601.

[4] 严雨、夏宁,Labview入门与实战开发100例(第三版),电子工业出版社,2017.

范毅,19790620,男,陕西咸阳,汉;大学本科;工程师;计算机应用

- 乡村振兴战略下苏州创新型乡镇发展现状及问题分析

- 关于乡村治理中村民自治问题的研究

- 传统村落经济社会转型与发展路径研究

- 村组集体经济组织债务管理存在的问题与对策

- 张掖市经济增长与耕地流失的库兹涅茨曲线假说

- 校园欺凌现象的行为分析与对策研究

- 陕西省养老机构体育服务的基础设施研究

- 人口老龄化对医疗保障的影响及对策研究

- 城市轨道交通CBTC系统仿真实验室设计

- 关于创新“互联网+工会”工作模式的探讨

- 政府会计制度改革及其对高校财务管理的影响

- 浅析化学品制造企业的财务风险防范与控制

- 关于加强公立医院固定资产管理的思考

- 网络化运营条件下地铁财务管理的初探

- 行政事业单位财务管理存在的问题及对策

- 浅谈行政事业单位会计核算存在的问题及应对措施

- 电力集团资金管理的困境和对策研究

- 侣太行山高速沿线区域红色旅游发展探析

- 中国文化“走出去”的影响因素及路径分析

- 我国中小企业人力资源管理外包问题探析

- 浅析大型国有煤炭企业人力资源结构调整工作

- 基于工作量核算模式的医院绩效考核模式研究

- 新形势下煤矿企业人力资源管理工作存在的问题及对策

- 经济“新常态”下人力资源管理方式的挑战与创新

- 创新驱动背景下物流企业比较研究

- jihads

- jilt

- jilted

- jilter

- jilters

- jilting

- jiltish

- jilts

- jingle

- jingled

- jingler

- jinglers

- jingles

- jingle²

- jingle¹

- jinglier

- jingliest

- jingling

- jinglingly

- jingly

- jinx

- jinxed

- jinxes

- jinxing

- jit

- 木橛子也能绊倒人

- 木母

- 木母金公

- 木气

- 木水辰儿

- 木池

- 木治

- 木滋滋

- 木火辰儿

- 木炭

- 木炭搭桥——难过

- 木炭画

- 木炭的通称

- 木焦

- 木然

- 木燃

- 木燧

- 木片

- 木片楔子

- 木版

- 木版水印

- 木版画

- 木牛流马

- 木犀

- 木犀草