邵忠俊 营旭东 秦岭 刘巍 潘宇波

【摘要】? ? 面对各种重要工作领域提出的要求,如航空航天、银行及电厂所要求的高安全行业,都对使用到的电子系统提出了更高的安全性要求。容错计算机的出现,进一步取代双机热备产品,出现在了高安全领域,从此掀开了高安全性电子设备的新篇章。设计一种高可靠的容错计算机,可应用于如航空航天、列车、银行及电厂所要求的高安全行业。

【关键词】? ? 双机热备? ? 冗余? ? 容错

一、结构冗余设计

1.1硬件结构冗余

该计算机从系统架构上采用2乘2取2结构,两个计算机系同时运行,一个拥有控制权,另一个只有监视权,在I端计算机系故障的情况下,II端计算机系取得控制权;两端的计算机系内各包含两个通道,分别为命令通道(A通道)和监控通道(B通道)两个通道。两个通道具有相同的硬件设计,采集相同的数据,运行相同的软件。通道内处理器模块通过局部CPCI总线访问接口模块。两个通道之间可通过CCDL或者以太网进行通信,双余度设计分别对两路输入信号和运算结果进行同步比较,只有两个运算结果一致时,该计算机系才会输出,否则控制权交由另一结构与之相同的计算机系输出结果,本机则马上发出报警信号并输出安全态。

1.2 软件结构冗余

命令通道(A通道)和监控通道(B通道)的软件系统结构框图1如下所示。

二、信息同步设计

基于信息冗余思想,采用软件为主,软/硬结合的双握手同步算法实现通道间的同步,两次同步的处理过程,能够确保计算机系内两通道工作流程的同步性,而两通道数据的一致性则通过数据同步流程实现,即两通道间处理器板在每一次数据交换时,增加周期帧信息,以此来保证系统失步后能在相同的周期内与另一通道重新同步。

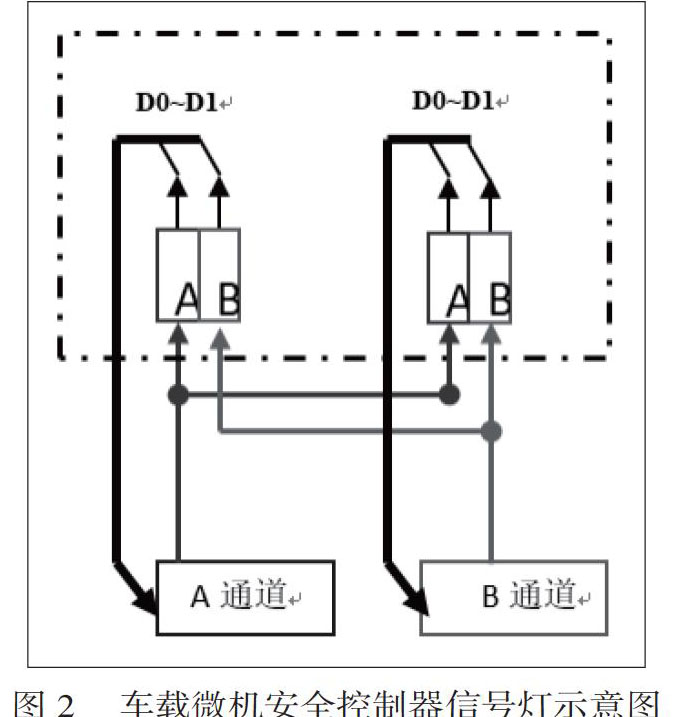

本案中两台计算机的同步设计可采用信号灯同步和数据同步方式相互结合的方式。其中信号灯同步:两台计算机通过相互交叉点亮和熄灭对方的信号灯实现同步,也就是“置位”和“复位”特定的信号存储单元。该方式能够做到任务周期的同步,是应用最广泛的同步技术,也叫“信号握手”(见图2);数据同步:在数据帧传输时,通过增加同步帧达到同步目的。该方式能够解决系统失步后的重新同步问题。

计算机系内的两个通道通过信号灯同步(包含初始同步和周期同步)和数据同步的方式实现任务同步。采用以软件为主,软/硬结合的双握手同步算法实现通道间的同步。

计算机同步的过程是在系统同步程序的管理下,结合硬件定时器,通过信号灯,完成通道间的同步。此信号灯同步方式通过软件对计算机系内两通道同步故障检测板内部相应寄存器进行“置位”和“复位”操作并比较结果实现。

初始同步:系统完成初始化、上电自检后,进入周期任务之前,计算机系的A、B通道要进行初始同步,初始同步的两次握手最大等待时限为2秒。该过程要清零看门狗计时器。当初始同步失败后,软件不再执行周期任务,在故障寄存器中记录初始同步故障,并交出系统的控制权。

周期同步:在每个工作周期开始时,A、B通道要进行同步握手,其最大允许等待时间为200微秒;在读取输入数据和对方计算结果后,要比较同步帧的一致性。周期同步过程不清零看门狗计时器。如果两个通道的周期同步失败,给周期同步失败计数器加1,并重新启动任务周期,若连续10次均同步失败,将不再执行周期任务,在故障寄存器中记录周期同步故障,并交出系统的控制权。

以上两种同步的方式区别在于初始同步解决两机同步启动问题,两次握手最大等待时限为2秒;周期同步解决应用任务的同步问题,最大允许等待时间为200微秒,故障寄存器记录10次故障后报错。重复次数和等待时间为设计经验参考值(下同),可根据用户需求调整。

数据同步是指两通道间处理器板在每一次数据交换时,增加同步帧信息,以此来保证系统失步后能在相同的周期内与另一通道重新同步。当发生数据同步错误时,可采用以下两种方式处理数据同步后的失步问题:1、强制将同步帧号中较大的同步帧号改为两者中较小的同步帧号,同时,数据同步错误计数器加1,任务继续向下进行。2、数据帧中较大的周期帧通道等待较小的周期帧通道指令,等待3个周期仍失败时,数据同步错误计数器加1,并重新启动任务周期。若同步连续10次均失败,将不再执行周期任务,在故障寄存器中记录数据同步故障,并交出系统的控制权,同步流程图见图2。两种同步帧失步后的处理方式可根据用户需求修改。

三、容错算法决策与安全态输出

产品的硬件冗余结构与其软件冗余结构相互配合,保证系统能够高可靠性工作。然而,这种高可靠性对输入信号或产品本身是极为“敏感”的,这种“敏感”极易造成产品输出出現瞬态错误现象。为了消除这种高可靠性引起的“敏感”特性,产品在各计算机系中的安全输出板,增加了一种软件“容错技术”,进一步增加产品的可靠性。

经计算机同步的两通道数据通过各自CPCI总线分别进入可编程逻辑模块中的CCQI及CCQII逻辑中,当CCQI及CCQII接收到对应通道的周期帧及有效数据后,接收数据标志信息位由‘0变为‘1,表示本逻辑已收到数据;当接收数据标志信息位都发生变化后,开始对比两有效数据的周期帧信息,若两者相同,则说明两组数据是同一时刻数据;当已经判断数据没有丢失的情况下,在CPU输出数据比较寄存器中,对两通道数据进行比较,若比较一致,说明两通道数据相同,CPU数据比较错误计数器减1;若比较不一致时,说明本系有故障,CPU数据比较错误计数器加1,当该计数器超过8时,输出导向安全态,从而实现容错策略。

两台计算机系输出控制权的切换由三个信号决定:外部给定的控制权、I端计算机系的故障情况和II端计算机系的故障情况。如果I端、II端计算机系都没有故障,则由外部设定控制权,确定计算机系输出(主控)端;如果I端、II端计算机系中有一个故障另一个正常,那么无论外部控制权在哪端计算机,系统都由无故障的计算机系输出,当主控计算机系故障时,系统要马上给出报警信号。

控制权计算部分根据两个通道的通道故障逻辑输入、另一个和控制权外部输入决定本控制器是否允许输出,并将该信号提供给安全输出板。

通道故障逻辑的输入为离散量,为提高可靠性,采用两位编码,bit1.0=10,表示逻辑0,bit1.0=01,表示逻辑1。

下表1是控制权切换逻辑的真值表。

四、结束语

1、系统采用2取2安全计算机结构,为系统的高可靠性要求,提供了必要的硬件基础平台;

2、计算机系内的两个通道通过信号灯同步和数据同步的方式实现任务同步。采用以软件为主,软/硬结合的双握手同步算法实现通道间的同步,增强了对采样数据对比的有效性;

3、安全输出板对有效数据再一次进行有效性比较;再一次确保有效数据的有效性;同时,针对偶发故障进行了一种容错逻辑处理,确保设备在允许范围内,不由于自身或外界的某些影响而产生不必要的输出切换或报警;

4、当出现系统故障后,安全输出板立刻将输出导向“安全态”,保证受控设备时时处于可控、安全状态。

参? 考? 文? 献

[1]容错控制系统的分析与综合[M]. 浙江大学出版社 , 葛建华,孙优贤著, 1994.

[2]控制系统的故障诊断和容错控制[M]. 机械工业出版社 , 闻新等著, 1998.

[3]王德军、故障诊断与容错控制方法研究[D].吉林大学,2004.

- 建筑施工企业财务内部控制问题及对策

- 房地产收并购业务财务风险管控

- 加强公立医院管理会计建设与实践的探讨

- 建筑施工企业财务风险控制研究

- 会计基础工作规范化管理的必要性及问题分析

- 财务管理在企业内部控制中的作用

- 浅谈企业现金流管理

- 高新技术企业成本管理困境与改善措施

- 新政府会计制度下的行政事业单位财务管理研究

- 企业财务管理风险及防范分析

- 上市公司会计信息披露相关问题探究

- 关于企业业财融合的思考

- 浅谈新政府会计制度下事业单位预算管理

- 民营企业资金管理的问题及对策

- 成本性态分析在造船企业费用预算中的运用

- 关于企业财务预算管理的一些思考

- 大数据视角下实施财务共享服务的思考

- 浅谈国有企业财务管理模式设计

- 对财政预算绩效管理工作改进的思考

- 浅析企业构建财务共享中心面临的问题及对策

- 土地整治企业的会计收入成本核算研究

- 企业财务报表分析的问题及对策探讨

- 行政事业单位财政支出绩效评价研究

- 浅析烟草商业企业资产管理存在的问题及对策

- 政府会计制度下公立医院实施全面预算管理分析

- broken through

- broken up

- broken²

- broken¹

- broke-off

- broke off

- broke-out

- broke out

- broker

- brokerage

- brokerages

- broker-dealer

- brokerdealer

- brokered

- brokeress

- brokering

- broker's

- brokers

- brokership

- brokerships

- brokery

- broker²

- broker¹

- brokes

- brokest

- 孝为百行之先

- 孝义

- 孝义难以两全

- 孝乌

- 孝于亲则子孝,钦于人则众钦

- 孝亲

- 孝亲之人子

- 孝亲之行

- 孝亲的典故

- 孝伯痛饮

- 孝假

- 孝先便腹

- 孝先眠

- 孝先经笥

- 孝养

- 孝养义母

- 孝养父母

- 孝养父母的准则

- 孝养父母,极意承欢

- 孝养长辈

- 孝化

- 孝堂

- 孝女

- 孝女江

- 孝妇冤