刘香 曾怀星 卢伦

摘要:利用Cadence Allegro SPB16.6介绍快速设计印刷电路板(以下简称PCB图)的一些技巧。例如使用快捷键、调用Skill插件、设置约束规则概要、器件封装数据库、多种手工布局等设计方法来提高PCB设计效率。叙述了设计PCB图时注意事项,如应用snap pick to功能,快速定位机械孔,放置安装孔等。

关键词:Cadence;快速;设计;PCB

中图分类号:TP302.1 文献标识码:A

文章编号:1009-3044(2020)21-0078-03

开放科学(资源服务)标识码(OSID):

1 引言

Cadence是EDA工具中属于高端的PCB设计软件之一。Cadence在原理图设计、PCB布局、布线、仿真、高速电路设计及EMI等方面有着绝对的优势。从事电子行业特别是经常采用此软件绘图的人员如何快速、准确地掌握使用Cadence快速设计PCB图的方法,是有一些技巧的。本文采用Cadence AllegroSPB16.6介绍快速绘制PCB图的一些技巧和注意事项。

2 快速设计PCB图的技巧

2.1 快捷键

熟练使用快捷键是快速设计PCB图的有效方法之一。Ca-dence系统是一个开放的平台,这对于采用此软件绘图的人员如何快速定义自己专用的且长期有效的快捷键是必要的。本文建议在本地环境变量文件中直接定义。找到安装目录下的本地的环境变量文件是evn文件(例如c:\pcbevn),可以通过“写字板”打开“env”文件对它进行编辑。alias命令可以在第二行开始写(第一行是:source $TELENV),例如Allegro布线时常用的如下定义:

funckey l options acon_line_width 10(设置走线lOmil)

funckey 2 0ptions acon_line_width 20(设置走线20mil)

funckey 3 0ptions acon_line_width 30(设置走线30mil)

funckey 4 0ptions acon_line_width 4泼置走线4mil)

funckey 5 0ptions acon_line_width 5(设置走线5mil)

funckey+ subclass一十f切换层递增)

funckey - subclass一(切换层递减)

funckey m show measure(测量)

funckey a add connect(走线激活)

funckey e done(平滑走线)

布局时的以下几个常用的shortkey:

alias Insert Define grid(i置栅格)

alias -E move(移动器件)

alias -R angle 90(器件旋转90度)

alias -F mirror(器件放置Bottom面命令)

alias End redisplay(屏幕刷新)

alias Del Delete(删除命令)

alias Home Zoom fit(全屏显示)

2.2 Skill插件命令调用

Cadence公司还开发了自己的编程语言skill,并为其编写了编译器。由于skill语言提供编程接口,Cadence公司认为是类C语言风格,所有的Cadence工具都是用Skill语言编写的。要快速设计PCB图,提供设计Skill插件命令调用这里采用将载人语句写入PCBENV目录下的allegro.ilinit文件内来实现Alle-gro启动时自动加载。

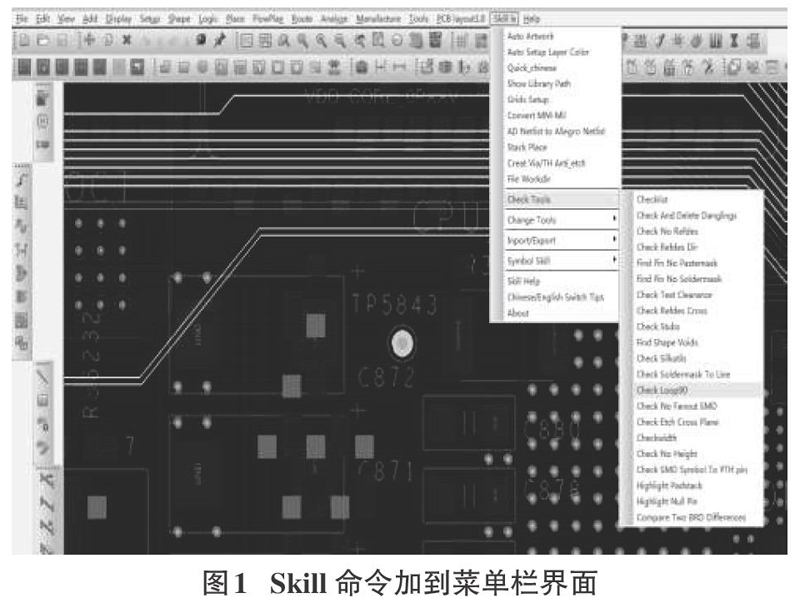

一般可以安装工程师自己编译的或者调用网上下载Skill。将Skill编好后,都带有一个执行命令,当调用该命令时,不可能每次都手动输入命令。最好的办法就是将Skill命令加入Alle-gro菜单中。Allegro带有一个菜单配置文件。可在安装目录下找到。比如我现在将Cadence安装在D盘,那么就在以下目录可加到菜单文件栏,详见图1。

Skill插件调用可以对Cadence设计工具进行许多功能的扩充,实现功能的定制,明显地提高工程师的设计效率。

2.3 约束规则的设置概要

设计过程要了解某PCB图用于何种场合,主要的功能,采用的核心芯片供应商和型号。目的是为了让PCB设计工程师尽快了解项目的需求,例如:

1)板名和版本号

2)希望的PCB叠层数

3)板厚

4)介质材料

5)板面积长( )X宽()mm(参考结构要素图)

6)期望的最小布线线宽是( )mil

7)期望的最小布线间距是( )mil

8)期望的最小过孔是( )mil

根据PCB图的基本參数迅速设置约束规则,点击“Setup→Contraints→Constraints manager”[1]即可进入。

2.4 器件封装数据库

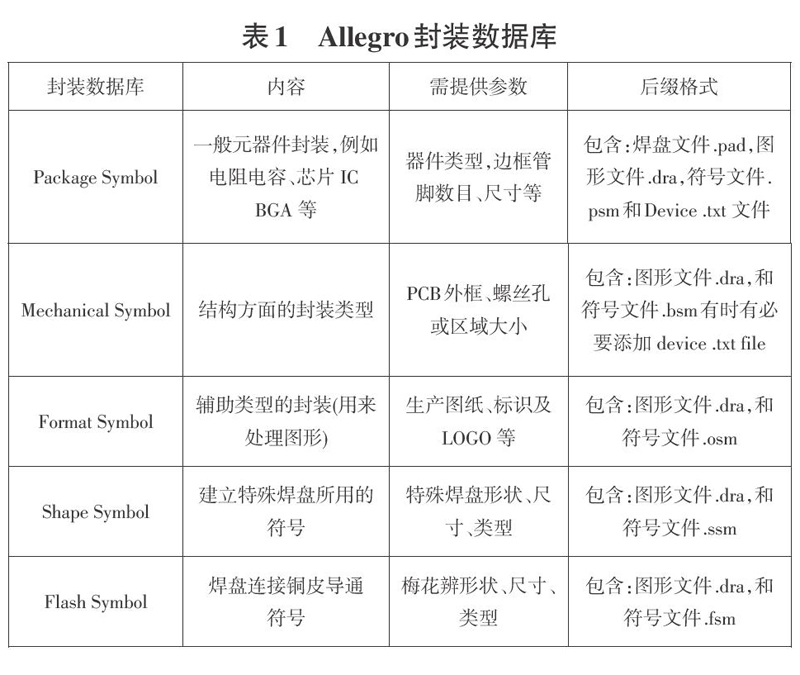

在Cadence的设计软件Allegro中封装数据库主要有Pack-age Symbol, Mechanical Symbol, Format Symbol, Shape Symbol和Flash Symbol封装类型,每种类型都有不同的用处。常用的是Package Symbol、Mechanical Symbol和Format Symbol。熟练掌握器件封装设计可以提高设计进度、提高器件库设计的可维护性。很多操作灵活运用,可以极大地提高PCB图设计效率。下表1为简单介绍封装数据库。

这时我们设计PCB图时,将此所需的器件从封装数据库调出即可,这样就节约时间。当然所有器件库虽已经过反复审核校对,但在初次使用时仍须仔细核对datasheet以确保准确无误,尤其是芯片库。

2.5 快速多种手工布局

使用Cadence快速设计PCB图的方法,布局是一个重要的环节。布局直接影响整个电路板的效果。布局也是设计电路板最花费精力的地方之一。那么就要求PCB图工程师能迅速的掌握Allegro布局的技术。

1)Allegro与OrCAD如何交互布局

根据信号传递方向放置其他元件,Cadence中Allegro与OrCAD可以实现交互布局,在ORCAD里设置,打开options/pref-erences,在Miscellaneous条目下,勾选intertool commumcatIon下的Enable Intertool Commumcation

即可以根据原理图信号流程实现PCB快速布局。

2)多种手工布局

Allegro Room布局;Allegro Page布局;Allegro模块设计复用布局[2]。见表2所示。

一般布局推荐使用20MIL网格,可以参考硬件工程师提供的原理图和大致的布局。根据页码、信号传递方向放置主芯片元器件,连线尽可能地短,关键信号线最短;一些元器件组成的功能模块可以按Room布局,对于相同结构电路部分采取Mod-ules布局且尽可能采取对称布局;布局注意分区,强弱信号、高电压信号和弱电压信号、模拟信号、数字信号要完全分开,高频元件间隔要充分。在保证电路功能特性的情况下,尽量按照均匀分布、重心平衡、版面美观的标准来优化布局。

2.6 布线

布线是PCB设计中最耗时的环节。布线需要遵循一定的规则,很多资料中都有提到[3]。不理想的布线会影响到电路功能的实现和电路板的性能。本研究利用Cadence中的Allegro如何快速PCB图布线。大家都知道Allegro的约束规则非常强大,设计高速线、差分线及其他关键网络等。随话说磨刀不怕砍柴工,规则设置前要了解以下知识点,事半功倍。

1)本PCB图的主要总线网络,了解其频率,是否有长度要求,误差多少mil以内,是否要走蛇形线。

2)差分网络以+/一或N/P作后缀,以利识别。差分阻抗( ohm)要求是多少。

3)其他关键网络,如模拟信号、复位信号等。

4)电源地树状图,电源地网络的特殊设计要求,如单点接地、静电泻放条、电源、地分割、挖空等要求。

3 设计PCB图时的注意事项

1)设计非金属化孔,可以在Pad Designer-parameter属性中plating选Non-PLated,在Drill diamter输入孔直径;同时设顶层和底层设置regular pad,中间层以及阻焊层和加焊层都是null。注意:regular pad要比drill hole大一点。考虑加工误差,一般来说,差值一般在4-20mil。

2)去偶电容布局时,尽量靠近芯片的VDD管脚,使VDD和GND之间形成的回路最短。当多个电容同时对一点滤波时,建议从小电容引出的线接到器件管脚。即靠近IC管脚的为最小的电容。

3)应用snap pick to功能,快速定位机械孔,放置安装孔。move-选元器件中心一右键snap pick to-Are/Circle Center -点就中,准确无误。

4)通常情况下的PCB电源的通流估算方法:外层铜厚10z时1A/mm线宽,内层0.5A/mm线宽,短线电流加倍,PCB铜箔的通流能力与它的宽度、厚度、温度有关,在空间不足的情况下增加铜箔厚度可增加电源的通流能力[4]。说明:如0.502可以1mm通流lA的话,10Z则可以Imm通流2A。

5)接地设计是解决EMC问题最廉价又有效的方法,在PCB设计阶段就应该充分考虑良好的接地方案[5]。

4 总结

快速设计PCB除了需要对所使用的软件特别熟悉之外,还要涉及其他方面的知识。本文只是根据笔者多年的工作中的经验积累,选择了一些最常用的要点进行了归纳,冰冻三尺,非一日之寒,随着实践经验的不断积累和自我不断学习,才能成为一名优秀的PCB设计师。

参考文献:

[1]周润景.Cadence PCB设计与制板[M].北京:电子工业出版社,2015.

[2]李美娴,梁仕章,黄晖,等.基于Cadence的模块化电路设计与应用研究[J].电子产品可靠性与环境試验,2019(S1):167-170.

[3]齐志强.高速PCB设计经验与体会[J].电子设计工程,2011(16):141-143.

[4]冲锋,胡书通,李兴文,等.PCB接触通流能力分析及评估软件开发研究[Jl,电器与能效管理技术,2014(16):1-5.

[5]陈兰兵.Cadence高速电路板设计Allegro SiUtiy SI/PI/EMl设计指南[M].北京:电子工业出版社,2014.

【通联编辑:梁书】

作者简介:刘香(1979-),女,江西樟树人,助理工程师,本科,主要从事电子信息工程技术相关技术研究。

- IOE联合镜像疗法在吞咽障碍患者中的应用探讨

- 超声引导下C6单点肌间沟臂丛联合颈浅丛阻滞在锁骨手术中的临床效果观察

- 小柴胡汤治疗椎动脉型颈椎病的疗效及对动脉血流速度的影响

- 我院病区药房退药情况调查及减少退药对策

- 温针灸结合低分子肝素钙对ICU患者下肢静脉血栓形成的影响

- HMGB1-Th17/IL-17炎症轴在重症肺炎中的作用及其临床意义

- 胃息肉患者检测幽门螺杆菌及血清胃蛋白酶原的临床意义

- 肺结核合并糖尿病不同抗结核治疗方案效果分析

- ALA-PDT联合苋草苏合剂对尖锐湿疣HPVDNA含量的影响

- 早期胃癌诊断治疗中消化内镜黏膜下剥离术的价值分析

- 首发未服药精神分裂症患者血浆IL-6水平与抑郁症状的相关性

- 左卡尼汀对维持性血液透析患者贫血状况、T淋巴细胞亚群和微炎症状态的影响

- 重症脑出血患者采用醒脑静与依达拉奉联合治疗的临床效果分析

- 穴位贴敷联合艾灸治疗肿瘤患者阿片类药物相关性便秘的效果

- 孕激素类药物对妊娠期糖尿病的影响

- 宫颈上皮内瘤变及早期宫颈癌组织中P16、HPVL-1壳蛋白的表达分析

- HBsAb/HBeAb/HBcAb阳性多发性骨髓瘤化疗后HBV再激活1例并文献复习

- 血清细胞因子水平检测在COPD急性加重期和稳定期的临床价值研究

- 导尿管长期留置患者尿培养病原菌分布及耐药性探讨

- 多层螺旋CT在急性脂垂炎的临床价值

- 超声与CT在小儿急性阑尾炎术前诊断中的价值比较

- 子午流注择时五音疗疾对30例老年原发性高血压低危组患者痰湿体质干预研究

- 老年结肠造口患者早期社会关系质量与希望水平的相关性研究

- 影视团体心理治疗应用于躯体形式障碍患者的护理研究

- “互联网+”新型健康教育模式对中青年高血压患者的影响研究

- confederation's

- confederations

- confederator

- confer

- conferable

- conference

- conferencecall

- conference call

- conference calls

- conferenced

- conferences

- conferencing

- conferential

- conferment's

- conferments

- conferrals

- conferred

- conferrences

- conferrers

- conferring

- confers

- confess

- confessable

- confessed

- confessee

- 改作

- 改俗迁风

- 改元

- 改元正位

- 改元正号

- 改写

- 改刀儿

- 改分门

- 改刊

- 改判

- 改制

- 改削

- 改动

- 改动地段的区划来谋取私利

- 改动成语、文件、古书等

- 改动,改换

- 改励

- 改化

- 改卜

- 改变

- 改变1

- 改变2

- 改变一个人的性格,比搬掉一座山还难

- 改变不良的文风

- 改变不良行为,重新做人