臧谱阳 王正斌

摘要:该文详细介绍了一种通过DDS数字合成器技术,来实现一种频率,幅度,相位可调制的高精度信号发生器。在FPGA中设计了串口模块和相应的解析模块向DDS发送指令,使其通过读取ROM内的波形数据存储器的数据进而实现对频率和相位的控制。同时可以根据需要自行更换ROM内存储的波形数据,能够产生正弦波,方波,锯齿波和任意波形信号。

关键词:FPGA;DDS;信号发生器;串口;ROM

中图分类号:TP311 文献标识码:A

文章编号:1009-3044(2020)27-0220-02

开放科学(资源服务)标识码(OSID):

1 概述

本系统以FPGA为核心控制器,相比于STM32系列单片机的顺序指令队列,FPGA强大的并行能力在处理模拟信号和拓展接口上效率会更高,读写速度也更快。相比于传统C语言通过FLASH读取数组信息来获取波形数据,本系统通过读取片内ROM并结合DDS进行波形数据采集,设计方法更加简单灵活,波形的显示也会更流畅。可以输出直流、交流等信号。

2 DDS技术原理与分析

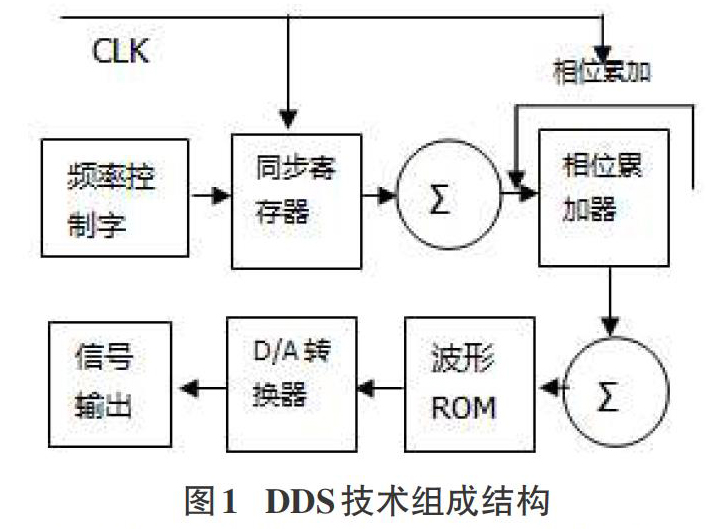

DDS(Direct Digital Synthesizer)是一种新型的频率合成技术,其主要组成部分有相位累加器,相位调制器,波形数据表和D/A转换器。其广泛运用于通信领域,特点是波形选择范围大,可供选择带宽的范围大,可控制时间长,精度高等[1-2]。对于信号的相位、频率、幅值均可以通过自制的波形编码生成,自由度大。其基本结构见图1所示。

在每个时钟的上升沿时,加法器会将默认的频率控制字与同步寄存器中的相位值累加,得到的数值是由加法器和寄存器的位数决定的。累加的值接着在第二个时钟上升沿时反馈至累加寄存器的输入端,重复与设定的频率控制字相加[3-5]。这样,在每一个时钟周期,对设定的频率控制字不断进行线性累加,这时的累加值输出的数据就是最终处理信号的相位值,也是波形存储器的采样地址。相位累加器的溢出频率,就是DDS输出的信号频率。通过查表找出相应相位的幅值,即可完成相位与幅度的数值转换。由于输出信号的幅度值是数字量,所以还需要将输出信号转至数模转换器中,将数字信号转变为模拟信号进行输出。

3 基于FPGA的信号源系统整体设计

3.1系统结构设计

整个系统的上位机由串口输入端构成,既可以选择PC机也可以选择单片机。MCU部分由FPGA和DA转换组成信号输出端。系统总体框架如图2所示。用户在上位机将所需的信号参数,波形通过串行总线发送给串口接收模块,串口模块接收到参数后对参数进行解析,并向FPGA发送DDS控制字。FPGA在通过接收、查表、输出的操作后就可输出对应的数字信号给数模转换芯片,经D/A芯片转换、滤波后就可得到模拟信号[6-7]。

3.2 FPGA的逻辑模块设计

FPGA是整个系统的核心默克,对整个系统的逻辑结构进行分配和整合。FPGA控制逻辑的整体结构如图3所示,主要完成以下功能:

1) PPL同步系统时钟;

2) 串口数据的接收和解析;

3) 向DDS模块单元发送控制字;

4) DDS模块读取ROM波形;

5) 为D/A转换提供时钟、数据以及相应接口。

3.2.1 DDS模块逻辑设计

DDS模块的时钟由PPL模块分频后可得到同步時钟,这里的DDS模块主要实现相位累加器和相位调制器。相位累加器是DDS能够实现的关键,为了保证波形的精度,通常会将位数设置的大一些。因此只需在每一个时钟周期将DDS控制单元传递来的频率控制字加上之前的值即可实现频率的变换[8]。同理,将相位控制字的数据读取到相位调制器中,加上相位累加器中即可实现相位变换。其顶层设计如图4所示。

3.2.2 波形ROM的设计

可通过matlab或者C将已经绘制好的波形数据存放在.mif文件中,然后调用Quartusll内的ROM专有IP核读取.mif文件,设置好端口位数和地址大小即可。

3.2.3 数模转换芯片和接口驱动

本系统选择的D/A转换芯片是ADI公司AD9767型DAC芯片,该芯片为双通道,14位、125Msps转换速率的高性能DAC芯片,输出形式为差分电流输出,输出电流满量程范围可设置为2-20mA。芯片本身自带1.2V的参考电压,无须外部提供参考源。

其原理图如图5所示。可以看出该芯片需要接收的信号为14位的数字信号和一个写信号WRT,在FPGA中可以直接接在ROM后。由于AD9767芯片的输出为电流型,输出范围为2-20 mA。而本系统需要的是电压信号,因此需要将AD9767芯片的输出电流转换为电压。可以通过两级运放先将电流转换为电压信号,再将电压信号进行放大,最后通过滑动变阻器调节放大倍数。

AD9767设有IOUTA和IOUTB2个通道,每个通道的输出电流值通过14位并行接口来设置,实时输出电流大小与并行端口输入的数字编码值DAC CODE以及输出满幅电流IOUTFS关系为:

IOUTA=(DACCODEl16384) XIOUTS

IOUTB=((16383 - DACCODE)/16384) X/ours

IOUTS为参考电流IREF的32倍,所以也可以通过外接电阻调节输出放大倍数[9]。

4 性能测试

对于信号源的要求,FPGA作为MCU与内部的波形表和数模转换器相连,实现波形数据的储存与时序控制,同时外接串口电路进行PC控制,通过内置的IP核与PC控制端进行数据交换。整个系统电路易于实现,经检验数值也满足实验的精度要求。

5 结语

利用FPGA逻辑处理的优势以及串口的稳定、迅速的优点,结合高精度模数转换芯片AD9767,设计了一种遵循模块化的多通道高精度信号源。系统通过用户所需的自定义波形,能够为实验人员提供更快更准确地提供幅值、频率可调的模拟信号。试验结果表明,该信号源系统的输出波形参数可控,波形光滑、幅值精度高、频率可靠稳定。

参考文献:

[1]王丹,李平,文玉梅,等.采用DDS频率合成的虚拟信号发生器研究[J].传感技术学报,2007,20(3):586-591.

[2]孙群,宋卿.基于DDS技术的便携式波形信号发生器[J].仪器技术与传感器,2009(4):69-70.

[3] Kent Gary W,ShengNeng -Haung.A High Purity, High-SpeedDirect Frequency Synthesizer [C].IEEE International Frequen-cy Control Symposium,1995:207-211.

[4]刘晨,王森章,直接数字频率合成器的设计及FPGA实现[J].微电子与计算机,2004,21(5):63-65.

[5]高书亮,黄智刚,杨东凯,基于DDS的BOC(m.n)信号发生器及其FPGA实现[J].数据采集与处理,2009,24(2): 243-247(2):243 -247.

[6]高琴,姜寿山,魏忠义.基于FPCA的DDS信号源设计与实现[J].西安工程科技學院学报,2006,20(2):210-214.

[7]曾云,韩顺锋.基于FPGA的DDS信号源设计及误差分析[J].舰船电子工程,2009,29(2):72-74.

[8] Taniz a R,JadiaK.High Density FPGA Based WaveformGenera-tion for Radars[M].IEEE Press ,2010.

[9]F.Cardells,J. Valls. Optimization of Direct Digital FrequencySynthesizer Based on CORDIC [J].IEEE Electronics Letters,2001,37(21):1278-1280.

【通联编辑:朱宝贵】

作者简介:臧谱阳(1995-),男,硕士在读,主要研究方向为电子科学技术;王正斌(1978-),博士,系主任,主要研究方向为电磁场技术。

- 影响PBL教学效果的主要因素

- 多媒体教室计算机管理与维护新探

- 基于DSP的农作物面积检测系统设计

- 西部地区大学英语课堂学习态度初探

- 某通信运营商集团客户经理绩效薪酬体系存在问题及对策研究

- 浅析Moodle平台高中信息技术课程设计

- 多媒体课件制作中应用Dreamweaver的探讨

- 基于模式的多层分布式软件系统架构的设计研究

- 浅谈有线电视系统的维护

- 论城市产业新区规划与电网规划衔接机制创新研究

- 浅析城市综合体智能化的现状以及发展

- 基于员工心理资本增值的工作绩效提升

- 更换ZXJ10B程控交换机服务器技术要点

- 湘南学院通信工程专业接受对口支援后的改革与探索

- 试论光纤通信技术在铁路通信系统中的应用

- 基于WiFi的商务酒店综合大楼无线网络设计研究

- 基于GIS的城市地下电力管网信息系统设计与实现

- 电力变压器无弧有载调压技术的分析与讨论

- 基于matlab的侧架摇枕铸造号的识别系统

- 现代通讯技术与通讯服务贸易的良性互动分析

- 基于OSPF和帧中继多点接口的网络工程教学案例设计

- 高职高专《计算机基础》课程教学模式思考

- 基于云存储视图库系统的并发性测试

- 基于S7-300PLC电厂循环水余热回收的控制系统设计

- 无线通信技术焦点分析与前景定位

- overhugely

- overhugeness

- overhugenesses

- overhuman

- overhumane

- overhumanities

- overhumanity

- overhumble

- over-humble

- overhumbleness

- overhumblenesses

- overhumbly

- overhung

- over-hunt

- overhunt

- overhunted

- overhunting

- overhuntings

- overhunts

- overhurried

- over-hurriedly

- overhurriedly

- overhurries

- overhurry

- overhurrying

- 铲除恶势力必须杜绝根本

- 铲除整饬

- 铲除杂草

- 铲除草根

- 铲除诛灭,杀戮

- 铲除豪强

- 铲除赖以生长的基地

- 铲除;去掉

- 铲革

- 铲马

- 铳

- 铳手

- 铳枪

- 铳炮

- 铴

- 铴锣

- 铵

- 银

- 银上万,无边岸

- 银丝

- 银丝挂面

- 银两

- 银两与绢

- 银丸

- 银主盘