摘 要: 为降低成本,提高设计灵活性,提出一种基于FPGA的1553B总线接口方案;采用自顶向下的设计方法,在分析1553B总线接口工作原理和响应流程的基础上,完成了接口方案各FPGA功能模块设计;对关键模块编写VHDL代码,并采用Active?HDL软件进行了仿真;以Virtex?5 FPGA开发板和PC机为验证平台,在FPGA中分别模拟BC与RT,在PC机指令下进行了BC与RT功能模块间的收发测试,结果表明系统能在协议规定的1 MHz数据率下稳定运行;同时,为提升接口性能,采用光纤代替传统电缆传输介质,利用FPGA内嵌RocketIO内核进行了传统1553协议数据的光纤传输,速率可达3 Gb/s以上。

关键词: 1553B总线; 接口; 现场可编程门阵列; 光纤

中图分类号: TN911?34; TP334 文献标识码: A 文章编号: 1004?373X(2015)03?0026?05

Design and verification of 1553B bus interface based on FPGA

PAN Peng?jun, ZHU Hao?wen

(Shanghai Aerospace Institute of Electronic Technology, Shanghai 201109, China)

Abstract: In order to reduce cost and improve design flexibility, a scheme of 1553B bus interface based on FPGA is brought forward in this paper. The design of all FPGA functional modules was completed with the top?down design method by analyzing the working principle and responding flow of 1553B bus interface. The VHDL codes were compiled for the key modules and simulated with Active?HDL software. BC and RT was simulated in FPGA, and the transmitting and receiving test of BC and RT was conducted through Virtex?5 FPGA development board and PC. The results show that the system works stable in 1 Mb/s data rate. To improve interface performance, the traditional transmission cable was replaced by optical fiber. The optical fiber transmission of the traditional 1553B protocol data was realized by embedding RocketIO core into FPGA through instead of copper cable. The data transmission rate is above 3 Gb/s.

Keywords: 1553B bus; interface; FPGA; optical fiber

0 引 言

MIL?STD?1553B[1](数字式时分制命令/响应型多路传输数据总线)由美国国防部于20世纪70年代末提出,它采用曼彻斯特编码方式和冗余的总线型拓扑结构,具有非常好的时钟同步能力及容错机制,极大地简化了电子设备之间的互联,因而被广泛应用于对可靠性要求较高的军事、航空、航天等领域[2]。

随着1553B总线优越性能不断体现,我国相关领域的应用需求不断增多,其关键地位也日益突出。但由于1553B协议本身较为复杂、国内技术相对落后,在1553B总线的设计中大多采用国外的协议接口芯片,典型如DDC公司的BU?61580等。一方面,这类芯片不仅价格昂贵,而且容易受国外限制;另一方面,在实际应用中,芯片许多功能略显多余,不能进行灵活设计。

现场可编程门阵列FPGA可将大量逻辑集成在单片IC中,其内部资源丰富,相应EDA开发工具功能强大[3],是理想的片上系统设计与实现平台。FPGA具有开发周期短、成本低、灵活性高等诸多优点,基于对协议规范的分析,通过FPGA来实现MIL?STD?1553B总线接口是可行的。本文提出了一种基于FPGA的1553B总线接口设计方案,并编写VHDL代码进行仿真,最后在FPGA上完成了设计验证,实现了传统1553B协议数据的1 Mb/s电缆传输和3 Gb/s以上光纤传输。

1 MIL?STD?1553B总线介绍

MIL?STD?1553B是一种命令/响应型多路传输总线,它采用冗余的总线结构,在当前传输线发生故障时可立刻切换到冗余传输线上,防止通信中断。同时,1553B协议严格规定了消息格式,限定了每条消息的最大传输数据量及总线单元的最大响应时间,并规范了总线耦合方式、电缆电气特性等,从各个方面确保总线传输的高可靠性。

1553B总线包含三种总线单元:总线控制器BC、远程终端RT和总线监视器MT,各单元在总线控制器BC的调度下有序地进行通信。总线上数据以字为基本单位进行传输,分为命令字、状态字和数据字,每个字包含20位。总线单元间每一次数据的交换称为一条消息,1553B协议规定了10种消息格式,除此之外其他格式的消息均为非法消息。总线采用曼彻斯特编码方式,方便接收端提取同步时钟,简化了总线结构[4]。

2 1553B总线接口整体设计方案

总线接口是外部系统与总线之间的数据交换媒介,其主要功能是完成总线协议的处理。根据1553B协议的特点,总线接口整体设计方案如图1所示。

由图1可知,总线接口包括模拟收发器、曼彻斯特编解码器和协议处理逻辑三大模块。其中,模拟收发器完成FPGA输出信号与总线信号之间的电平转换,可由专用转换芯片完成,而曼彻斯特编解码器和1553B协议处理逻辑是接口的主要组成部分,完成数据编解码和协议处理,通过FPGA实现。总线接口通过一定的地址、数据和握手信号与外部系统相连。

3 曼彻斯特编解码器模块设计

3.1 1553B总线数据格式

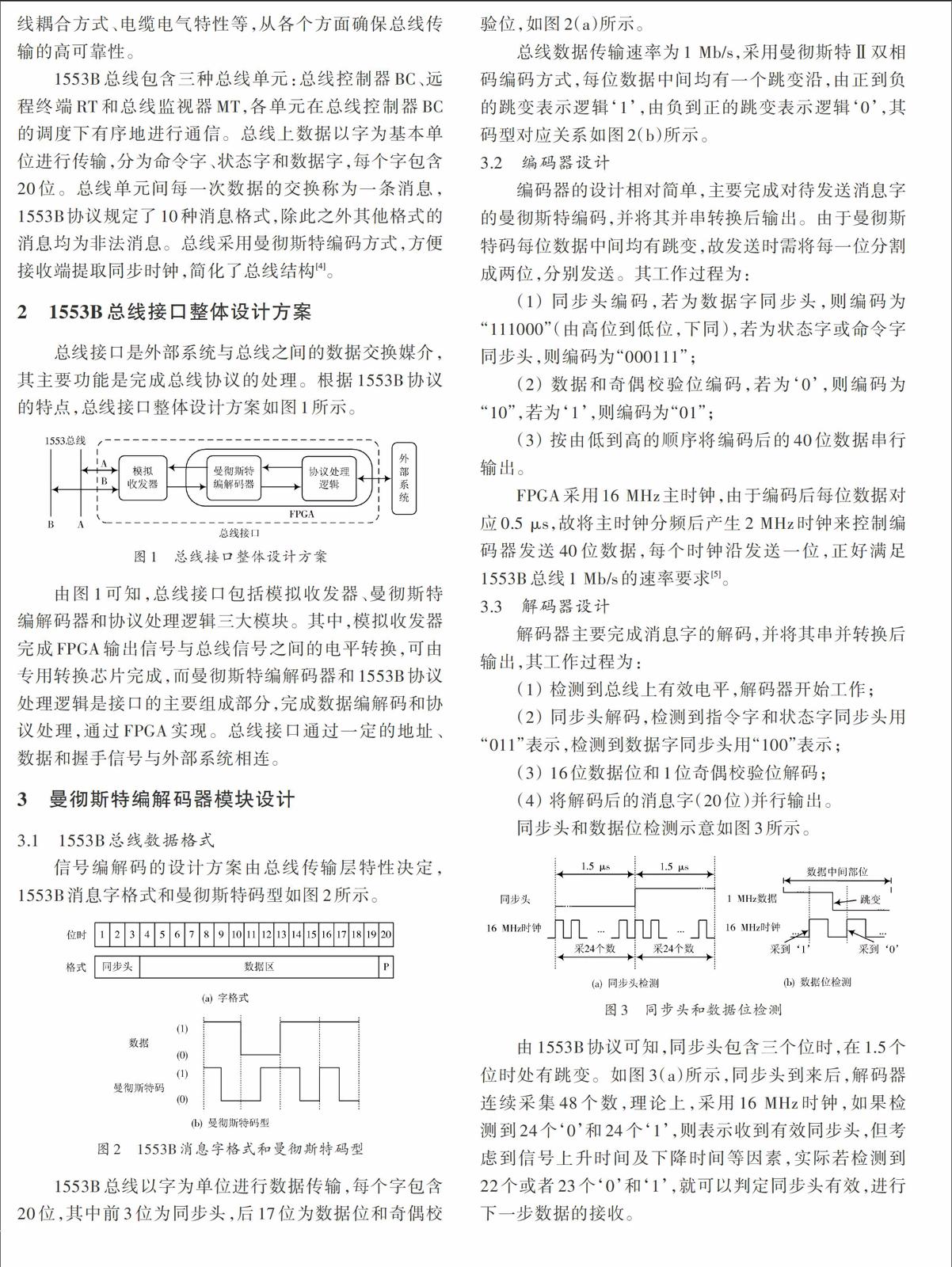

信号编解码的设计方案由总线传输层特性决定,1553B消息字格式和曼彻斯特码型如图2所示。

图2 1553B消息字格式和曼彻斯特码型

1553B总线以字为单位进行数据传输,每个字包含20位,其中前3位为同步头,后17位为数据位和奇偶校验位,如图2(a)所示。

总线数据传输速率为1 Mb/s,采用曼彻斯特Ⅱ双相码编码方式,每位数据中间均有一个跳变沿,由正到负的跳变表示逻辑‘1,由负到正的跳变表示逻辑‘0,其码型对应关系如图2(b)所示。

3.2 编码器设计

编码器的设计相对简单,主要完成对待发送消息字的曼彻斯特编码,并将其并串转换后输出。由于曼彻斯特码每位数据中间均有跳变,故发送时需将每一位分割成两位,分别发送。其工作过程为:

(1) 同步头编码,若为数据字同步头,则编码为“111000”(由高位到低位,下同),若为状态字或命令字同步头,则编码为“000111”;

(2) 数据和奇偶校验位编码,若为‘0,则编码为“10”,若为‘1,则编码为“01”;

(3) 按由低到高的顺序将编码后的40位数据串行输出。

FPGA采用16 MHz主时钟,由于编码后每位数据对应0.5 μs,故将主时钟分频后产生2 MHz时钟来控制编码器发送40位数据,每个时钟沿发送一位,正好满足1553B总线1 Mb/s的速率要求[5]。

3.3 解码器设计

解码器主要完成消息字的解码,并将其串并转换后输出,其工作过程为:

(1) 检测到总线上有效电平,解码器开始工作;

(2) 同步头解码,检测到指令字和状态字同步头用“011”表示,检测到数据字同步头用“100”表示;

(3) 16位数据位和1位奇偶校验位解码;

(4) 将解码后的消息字(20位)并行输出。

同步头和数据位检测示意如图3所示。

由1553B协议可知,同步头包含三个位时,在1.5个位时处有跳变。如图3(a)所示,同步头到来后,解码器连续采集48个数,理论上,采用16 MHz时钟,如果检测到24个‘0和24个‘1,则表示收到有效同步头,但考虑到信号上升时间及下降时间等因素,实际若检测到22个或者23个‘0和‘1,就可以判定同步头有效,进行下一步数据的接收。

数据位包含一个位时,在0.5个位时处有跳变。如图3(b)所示,在每个数据中间部位,若前一时钟采样到‘0,后一时钟采样到‘1,则表示当前数据位为‘0,反之则是‘1。另外,如果采到的数没有跳变,为全‘0或者全‘1,则产生错误标志,通知协议处理逻辑或子系统进行相应的错误处理。

4 协议处理模块设计

4.1 协议处理模块响应流程

协议处理模块实现BC,RT,MT三种总线终端的协议处理,在FPGA模块设计之前,根据1553B协议对协议处理模块三种工作模式下的响应流程分别进行分析设计。

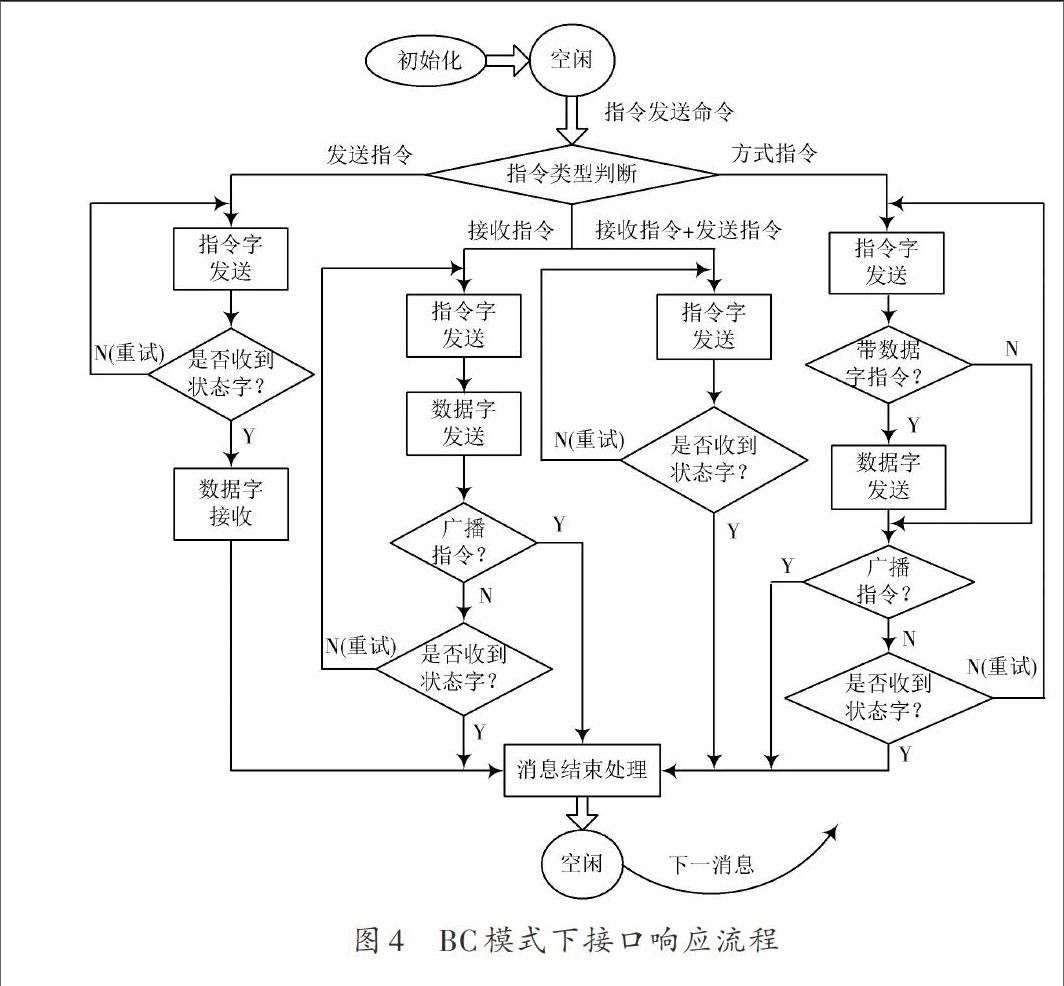

4.1.1 BC模式[6]

BC(总线控制器)是1553B总线的核心,总线上任何类型的数据交换都由它发起。BC模式下接口响应流程设计如图4所示。

MIL?STD?1553B协议规定的总线指令可分发送指令、接收指令和方式指令三种,共能实现四种类型的功能:RT到BC的数据传输、BC到RT的数据传输、RT到RT的数据传输和总线管理。根据图4,BC模式下接口主要工作过程为:

(1) 根据外部系统需求发送相应命令字,发起总线传输;

(2) 根据指令类型的不同,进入不同响应流程,主要包括数据字发送、数据字接收和状态字接收等;

(3) 消息完成后进行消息结束处理,主要包括消息结束标志的产生,差错处理,以及根据收到的RT状态字判断总线终端状态等。

需要注意的是,BC如果在规定的时间内没有收到RT状态回复,则需重新发送命令字进行重试(Retry)。

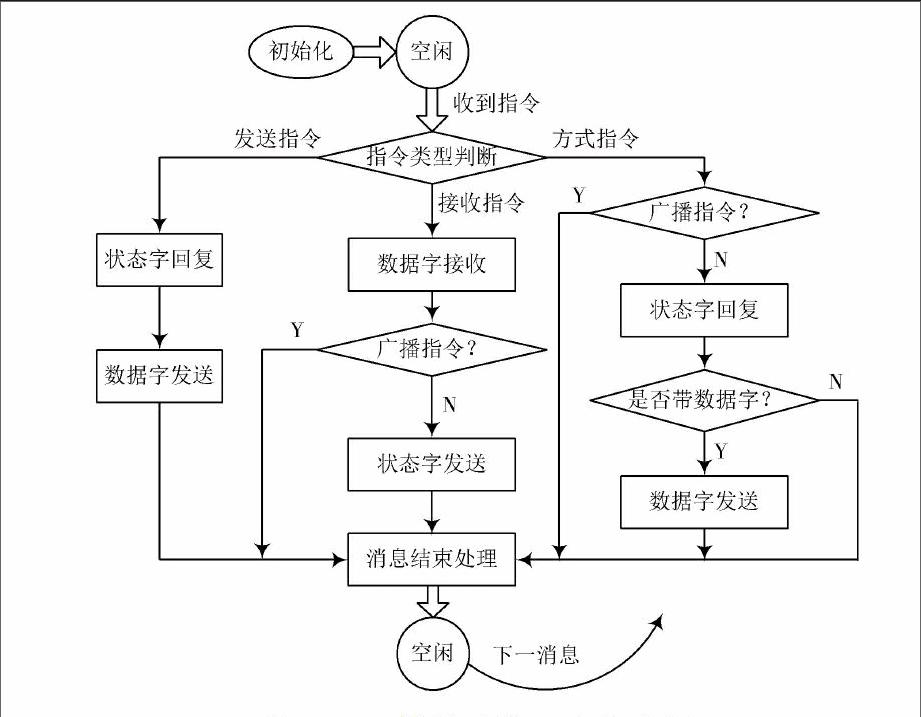

4.1.2 RT模式[7]

RT(远程终端)是1553B总线上的指令/响应型终端,它响应BC发送的指令,按要求接收或发送数据,在规定时间内回送状态字,并服从BC的总线管理。RT模式下接口响应流程设计如图5所示。

图5 RT模式下接口响应流程

根据图5,RT模式下接口主要工作过程为:

(1) 收到命令字后进行指令分析,根据指令类型进入相应的响应流程;

(2) 按照流程进行数据字接收、发送,并回复状态字;

(3) 消息完成后进行消息结束处理,主要包括消息结束标志的产生,差错处理,以及特殊方式指令下方式标志的产生等。

4.1.3 MT模式

MT(总线监控器)是总线上的监听单元,它监控总线上的信息传输,完成对总线的上原始数据的记录,但它本身不参与总线的通信。

MT模式接口的功能较为简单,主要进行指令字、状态字和数据字的接收并将其写入相应缓存中,方便以后提取分析,可通过BC模式或RT模式下接口相应的子模块实现。

4.2 协议处理模块FPGA总体设计

根据以上三种模式下接口响应流程的分析,对协议处理模块各FPGA子功能模块进行了划分[8],总体设计框图如图6所示。

协议处理模块主要由数据接收部分、数据发送部分和数据缓存部分组成,此外还包括超时检测、地址译码及读写控制、中断管理等辅助部分。由于三种模式下某些功能重复,为了提高FPGA资源利用率,设计时充分考虑了相应模块的模式复用,整个协议处理逻辑可在外部模式选择信号的控制下工作在BC,RT和MT模式。

图6 协议处理模块总体设计框图

16 MHz的全局时钟通过时钟管理模块为各FPGA功能模块提供工作时钟,各模块间通过一定的握手信号互联,保证协议处理逻辑有序工作。整个协议处理模块的基本工作原理如下:按照1553B协议规范,通过接收器接收总线上的数据并存入缓存,通过发送器取出缓存中的数据并发送到总线上,同时不断以中断和握手信号与外部系统进行通信,通知外部系统向缓存中写入待发送数据或从缓存中读取已接收数据,并共同完成差错处理和协议逻辑的管理[9]。

5 设计仿真与验证

根据设计方案,编写了重要模块的FPGA代码,模拟实现BC功能和RT功能,采用Active?HDL软件仿真,其中BC向RT的数据传输仿真结果如图7所示。

仿真通过后,在Virtex?5 FPGA[10]平台上对设计进行了验证,如图8所示。将BC功能模块和RT功能模块的代码经ISE综合、布局布线后分别下载到两块开发板中实现,开发板通过串口与PC机通信。PC机将指令和数据写入FPGA相应寄存器中,BC和RT在PC机指令的控制下进行1553B协议通信。验证过程中通过示波器查看模拟总线的波形,并通过ChipScope观察和比对协议收发数据。

验证结果表明,BC和RT功能模块能够正常按照1553B协议进行数据的发送和接收,完成基本1553B协议的处理,实现1553B协议数据的1 Mb/s电缆传输和3 Gb/s以上光纤传输,数据比对无误,说明该接口设计方案实际可行,具备开发应用价值,同时也为光纤1553接口的设计提供了一定参考价值。

6 结 语

本文提出一种基于FPGA的1553B总线接口方案,该接口采用模块化和通用性设计,能够工作在BC,RT和MT三种模式,实现曼彻斯特编解码,并完成1553B协议的处理。编写VHDL代码对设计方案进行了仿真和验证,证明了其可行性,同时对光纤1553接口的设计进行了探索性研究。目前,1553B接口芯片主要依赖进口,若能积极开展该方面的研究,开发出具有自主知识产权的通用IP核,对于摆脱国外限制,降低成本,提升我国在该领域的自主竞争力具有重要意义,其应用前景非常广泛。

本文创新点:将FPGA技术应用于1553B总线接口,缩短了设计周期,降低了设计成本,同时,系统的集成度提高,扩展性增强,设计灵活性也大大提高。

参考文献

[1] Department of Defence. MIL?STD?1553B: Military standard digital time division command/response multiplex data bus notice 2 [S]. USA: Department of Defence, 1978.

[2] 曹厚平.1553B总线系统的可靠性研究[J].科技与企业,2012 (5):91?93.

[3] 潘松,黄继业.EDA技术与VHDL[M].北京:清华大学出版社,2009.

[4] 李鹏,郑宾.基于FPGA的MIL?STD?1553B总线控制器的设计[J].电脑知识与技术,2012(1):217?220.

[5] 汤晓曦,尹蕾,许晏,等.基于FPGA的曼彻斯特编解码器设计[J].电子设计工程,2011(23):177?179.

[6] 颜学龙,黄雪明,任登娟.1553B总线接口控制器研究与顶层设计[J].微计算机信息,2007(22):36?38.

[7] 李宪强,周昌义.基于IP核的1553B远置终端设计[J].微计算机信息,2010(26):136?137.

[8] DDC. MIL?STD?1553B designer guide [S]. USA: DDC, 1998.

[9] 赵明阳,朱岩,张建东,等.基于PCI局部总线的1553B总线接口卡设计[J].现代电子技术,2012,35(10):55?57.

[10] Xilinx. Virtex?5 FPGA RocketIO transceiver user guide [S]. USA: Xilinx, 2009.

[11] 林强,熊华钢,张其善.光纤通道中的1553总线技术[J].航空电子技术,2004(1):1?5.

[12] 史林锋,王斌永,何志平,等.基于FPGA和BU?65170的1553B远程终端设计与实现[J].现代电子技术,2013,36(14):65?69.

[13] 李海军,牟俊杰,孙海文.高速1553B总线控制器通信管理系统设计[J].现代电子技术,2014,37(17):16?18.

- 认知视角下初级阶段留学生的汉语学习动机与学习策略

- 教育研究方法课教师实施当堂达标教学的教育叙事

- 地方高校经济学专业实践教学研究

- 校院两级管理下大学生心理危机干预机制的构建

- 大学生群体自我认知偏差研究

- 论高校思政课马克思主义生态文明 思想教学的“五课联动”机制构建

- 大众传媒语境中的“课程思政” 与“文艺载道”论

- 基于教务管理系统的高校 教务工作优化与创新

- 高校外教管理的问题和对策

- 形成性评价在理论经济学课程 考核中的应用

- 大学生社会实践校地共育模式 创新与实践

- 高校专业课教师参与第二课堂机制研究

- 高校创新创业教育研究现状及 立体闭环构建设想

- 人类命运共同体视域下大学生 责任意识的培养

- 传统生态智慧进校园的路径

- 高校思想政治理论课 创新思维能力的培养

- 硕士研究生毕业论文选题探究

- 新时代大学生宿舍人际交往 及调适之探索

- 本科生导师制:高等教育质量 提升的新探索

- 关于高校思想政治理论课 青年教师教学能力提升的思考

- 创新创业教育下高校教师专业发展研究

- 促进教师在职业道德建设中 发挥主体作用的研究

- 后现代语境下高校青年教师 自主专业发展途径探讨

- 高校师范生从生到师角色转换策略研究

- 大学英语课堂教学中教师语码转换的研究

- reengrave

- re-engrave

- reengraved

- reengraves

- reengraving

- re-enjoy

- reenjoy

- reenjoyed

- reenjoying

- reenjoyment

- re-enjoyment

- reenjoyments

- reenjoys

- reenlarge

- reenlarged

- reenlargement

- reenlargements

- reenlarges

- reenlarging

- reenlighten

- reenlightened

- reenlightening

- reenlightens

- reenlisted

- reenlisting

- 松骨头

- 松鬼

- 松鸡

- 松鸣岩“花儿会”的传说

- 松鸦

- 松鹤

- 松鹤延年

- 松鹤延龄

- 松鹤遐龄

- 松鼠

- 松鼠想吃树上鸟

- 松鼠的尾巴

- 板

- 板上钉钉

- 板上钉钉——一锤子敲定

- 板上钉钉——没跑

- 板上钉钉——跑不了

- 板上钉钉板上砸钉

- 板书

- 板了

- 板仓

- 板儿

- 板儿平

- 板儿条

- 板儿爷