摘 要: 太阳射电观测系统提出信号频段跨度大、观测频点多且频率及频点带宽可变、高精度多通道信号时间同步等要求。在此研究并采用奈奎斯特中频采样、多通道并行数字正交解调、滤波抽取得到数字基带信号。给出适合高倍率抽取的级联高效滤波器结构和易于工程使用的CIC滤波器幅度补偿方法。采用可编程延迟器实现系统高精度时间同步要求。完成了基于FPGA的硬件编程与硬件资源评估,使用线性调频信号作为测试信号在评估板上进行实际测试。结果表明在不同工作模式下,400 MHz带宽信号在脉冲重复时间内可被滤波抽取输出16路带宽可变的窄带正交基带信号,通带幅度平坦度、相位正交度等指标符合系统要求。最后讨论了硬件资源使用情况和潜在的性能升级空间。

关键词: 多通道观测系统; 数字接收机; 数字正交解调; 现场可编程门阵列

中图分类号: TN957.52?34 文献标识码: A 文章编号: 1004?373X(2015)07?0052?06

0 引 言

射电观测是人类研究天体的一个十分重要的手段。射电辐射能反映辐射体的重要特性和形状,不同波段的无线电波能反映出不同的特性和状态[1]。近几十年来,一些发达国家相继建立了自己的射电观测设施,广泛开展了射电观测活动,发展迅速,取得了一系列重要研究成果。我国射电观测活动开展较晚,但具有后发优势,采用当今最新的天线、无线电、模拟及数字信号处理技术,可建立功能更先进的射电观测设施[2]。本文主要研究了太阳射电信号数字接收处理方法。

1 系统组成及功能要求

射电观测系统采用综合孔径成像技术,通过若干在地面呈线型、星型或双螺旋分布的天线阵列接收太阳辐射,然后对多通道信号做互相关并积分得到复可见函数,最后通过傅里叶反变换得到辐射源亮度分布。射电观测系统通常工作在厘米波段(2~15 GHz)和分米波段(0.4~2 GHz)两个波段。本文讨论分米波段(0.4~2 GHz)观测系统由60台天线呈线性分布构成的干涉阵列,60通道信号接收处理机,以及系统相关处理与控制终端等组成,以高空间和高频率分辨率对太阳进行射电成像观测。

图1为分米波段太阳射电观测系统框图,系统主要由天线、模拟前端、数字接收和数据处理几部分组成。系统工作时,天线跟踪太阳并接收来自太阳的射电信号,经过电光转换由光纤传送到信号接收与预处理分机[3],变换为所需带宽的数字信号后传送至相关处理分机做相关成像处理。由于所观测信号带宽较大,若同时完成60台天线信号之间复相关运算,所需运算量和相应的设备量巨大,为了降低实现难度和成本,采用分时分子频段观测方式。

图1 分米波段日像仪系统组成框图

为获得良好的相关观测结果,系统要求观测时间间隔小,观测频点及带宽模式可选,各通道观测数据在时间上严格同步。结合目前电子技术和实现难度综合考虑,系统主要技术性能要求如下:一次全频段观测时间为100 ms,采用8 b,1 GHz模/数转换精度和速率;共划分为4个子观测带频段,每个子观测带频段带宽为400 MHz,观测时长3 ms;每个子观测带内设16个观测频点且中心频率可变,带宽在2 MHz,4 MHz,6 MHz,8 MHz,10 MHz模式之间可切换;各通道信号时延补偿范围为0~10 μs,补偿精度不大于1 ns,精度越高对相关运算越有利;系统工作模式切换响应时间小于5 ms。

2 数字接收处理分机

2.1 数字接收处理分机功能及组成

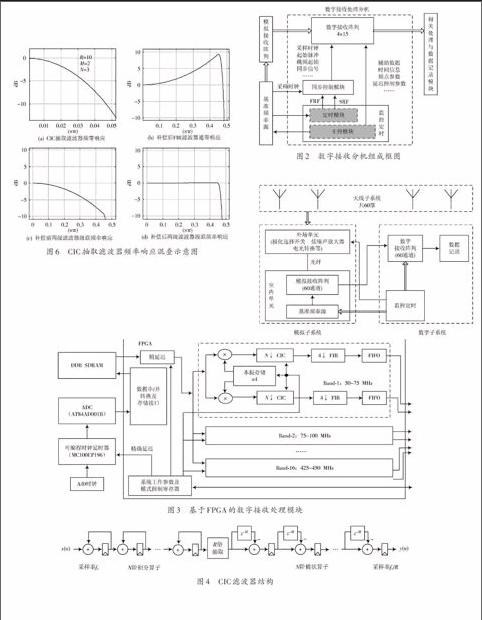

数字接收分机完成60通道中频信号(50~450 MHz)的模/数转换、数字带通滤波、数字正交解调、2 b量化及同步延迟等处理任务,得到每通道64个频点的复相关数据。复相关数据及相应的功率信息经格式化处理后送相关处理模块进行相关处理,并将相关处理结果送数据记录单元。数字接收分机的组成框图如图2所示。

同步控制模块以基准频率源的时钟信号及定时器的定时信号为基准,产生数据接收阵列60通道数据采集通道同步工作所需的采样时钟、采样起始信号及同步信号等,保证60通道数据采集通道的相位一致性。数字接收阵列的功能是完成来自模拟接收阵列的60通道信号的模/数转换、数字带通滤波、数字正交解调、2 b量化及延迟调整等处理。

图2 数字接收分机组成框图

数字接收阵列由15个数字接收模块构成,每个数字接收模块完成4个通道中频模拟信号数据采集。为了减少器件数量,采用Atmel公司生产的双ADC的模/数转换芯片AT84AD001B;采用一片高性能的FPGA来实现两个接收通道的信号数字接收处理功能,这样一个数字接收模块有2片A/D转换芯片和FPGA芯片。4个接收通道的复相关数据及功率信息和通道号、时间标志等辅助信息打成一个格式化的相关数据包,以串行LVDS接口形式发送给相关处理模块。此外还有半双工的串行监控定时接口,主控计算机将延迟调整、矫正相位及各种滤波器参数等系统控制参数发送给各个数字接收模块;接收来自各个数字接收模块的监测信息,监控各模块的工作状态。

2.2 基于FPGA的数字接收分机实现

图3为基于FPGA的射电观测系统数字接收与处理模块。主要完成功能为:400 MHz带宽信号经过16个多模式混频滤波抽取单元处理,变为间隔25 MHz的16个采样子频带信号,2 b量化后送入复相关处理模块进行相关成像运算;在系统监控模块控制下,调整粗延迟和精确延迟时间,确保60通道信号采样时刻严格同步。

2.2.1 A/D转换接口与缓存

由子观测带观测时间长度为3 ms和采样速率为1 GHz,可知每个子观测带信号数据量为3 Mb。目前FPGA片内存储容量较小,需要采用外置DDR?SDRAM存储器缓存数据。400 MHz带宽中频信号经过AT84AD001B芯片模/数转换,输出到FPGA为解复用后的2路500 Mb信号。经过FPGA内置Select I/O接口模块串/并转换将速率进一步降为4路并行的250 Mb数字信号写入片外SDRAM缓存。

2.2.2 混频

从400 MHz带宽信号中提取16个窄带信号过程为:将所需频带信号经过混频搬移到0中心频率,经过低通滤波滤除其他频率分量,根据信号带宽抽取到相应采样率即可。从片外缓存读取数据给16路混频滤波单元。系统要求每路子观测频带中心频率在一定范围内可变,为方便实现,在一个子观测频带内选择5个整数频率作为可选本振频率,如第一个子观测频带内为55 MHz,60 MHz,65 MHz,70 MHz,75 MHz。这样每个本振信号为不超过200个周期的数字序列,可预先存储在片内,混频时循环读取即可。

2.2.3 滤波抽取

每个观测子频带频点信号要求在2 MHz,4 MHz,6 MHz,8 MHz,10 MHz五种带宽之间选择,不同带宽对应不同采样率,是一个多速率信号处理过程。例如2 MHz基带I,Q信号采样率需要从1 Gb/s经过500倍降采样到2 Mb/s。这样如果采用FIR低通滤波器实现,通带相对带宽仅为0.002,满足通带阻带性能要求的滤波器阶数将达上千阶,滤波效率低且实现困难。文献[4]提出的高效滤波结构只是减小了计算量,降低了对器件处理速度的要求,并没有大幅度减小高倍抽取情况下硬件资源使用量。高倍数、多速率信号抽取插值采用级联积分梳状(CIC)滤波器实现,可节省硬件资源[5?6],CIC滤波器结构如图4所示。

CIC抽取滤波器是一种基于零极点相抵消的FIR滤波器,由积分算子和梳状算子两部分组成,其传递函数如式(1)所示,频率响应如式(2)所示。

[H(z)=HNIHNC=(1-z-RM)N(1-z-1)N] (1)

[H(z)=sin(πMf)sin(πfR)N] (2)

式中:[N]为滤波器积分梳状算子级联个数;[R]为抽取率;[M]为差分延迟;[f]为相对于抽取后信号采样率的归一化频率。

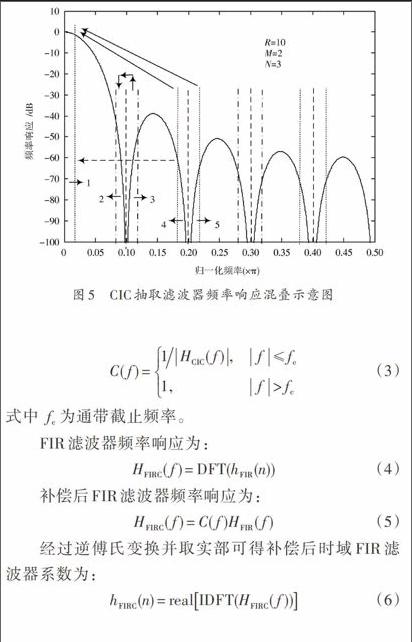

CIC滤波器的特点是实现结构简单,只需延迟和加减运算,硬件实现容易、资源占用少。但其缺点是通带平坦度差,高频衰减大,阻带衰减小且下降缓慢[7]。本文根据射电观测系统工作特点和参数要求,同时考虑到节省硬件资源消耗、实现难度等因素,采用两级滤波抽取方法完成高倍多抽样率数据处理。第一级使用CIC滤波器,针对不同带宽模式进行高倍可变倍数低精度滤波抽取,第二级使用常规FIR滤波器,进行低倍数高精度滤波抽取,并对第一级一定范围内的带内衰减进行补偿。这样有用信号频谱处在CIC滤波器通带低频频段,相对幅度衰减失真较小,且受到抽取导致的频谱混叠干扰影响也较小,CIC抽取滤波器频率响应混叠如图5所示。

图5所示为一个抽取率10倍、1个单位延迟、3个算子级联的CIC抽取滤波器频率响应混叠示意图。10倍抽取后0~0.1π(归一化频率)主瓣信号将扩展至0~π,主瓣后的旁瓣将依次正反混叠到主瓣频段内。假设第二级抽取率为5倍,则最终所要得到的有用信号频段为0~0.02π,即箭头所示第1频段,第3频段将混叠到第2频段上,第4,5频段混叠到第1频段上。这样相对于有用信号频段,第4,5频段信号为混叠干扰信号,从图中可以看出其最大幅度约为-60 dB,满足衰减要求。

图5 CIC抽取滤波器频率响应混叠示意图

两级滤波抽取优势是:CIC滤波器通带低频端幅度衰减小,且受到抽取后频谱混叠干扰小;第二级FIR滤波器滤除无用频段信号后,抽取即可得到有用信号。在抽取率比较小时,常规FIR滤波器只需较小的阶数即可获得较好的频率响应特性,一定程度上弥补了前级CIC滤波器的缺点。CIC滤波器低频端幅度衰减失真已有许多级联滤波器补偿方式,如锐化滤波器、余弦补偿滤波等方法,需要经过计算构造所需响应滤波器系数或需要单独级联补偿滤波器,还可能引起阻带衰减起伏[7?10]。本文提出一种更为简单直接的方法,根据第一级CIC滤波器有用信号频段内衰减曲线,直接对第二级滤波抽取FIR滤波器相应频段频率响应进行补偿,傅里叶逆变换后取实部,得到补偿后的FIR滤波器时域系数。由于舍去了虚部,带来了一定的相位非线性误差,经过仿真分析,在10 dB补偿幅度范围内,相位误差值不大于[10-7]度,可以忽略不计。由式(3)可得频域补偿系数:

[C(f)=1HCIC(f),f≤fc1,f>fc] (3)

式中[fc]为通带截止频率。

FIR滤波器频率响应为:

[HFIRC(f)=DFT(hFIR(n))] (4)

补偿后FIR滤波器频率响应为:

[HFIRC(f)=C(f)HFIR(f)] (5)

经过逆傅氏变换并取实部可得补偿后时域FIR滤波器系数为:

[hFIRC(n)=realIDFT(HFIRC(f))] (6)

图6为补偿前后CIC、FIR滤波器和两级滤波器合成通带频率响应曲线仿真结果。CIC滤波器参数分别为[R=10,M=2,N=3,]FIR滤波器使用131阶凯塞窗函数,截止频率为[π2。]对应的CIC滤波器中截止频率为0.05π,最大衰减约为-12 dB。未补偿的两级滤波器通带总频率响应衰减比较严重,补偿后基本实现了通带无明显衰减。

图6 CIC抽取滤波器频率响应混叠示意图

射电观测系统每个子观测带频率要求5种工作带宽2 MHz,4 MHz,6 MHz,8 MHz,10 MHz,中频A/D转换速率为1 GHz,对应的基带I、Q信号抽取率分别为500,250,166,125,100倍,将高倍抽取放在第一级CIC滤波抽取完成,对应抽取率为100,50,33,25,20倍。第二级为FIR固定倍数滤波抽取,考虑到滤波器过渡带宽度等影响将抽取率由5改为4,即1.25倍的过采样率,这样最终总抽取率变为400,200,132,100,80倍。Xilin?FPGA?ISE设计工具中提供了CIC和FIR滤波器IP核生成器,可生成参数可调、可变倍数的CIC滤波器和FIR滤波器模块。CIC滤波器参数中M,N参数越大,阻带衰减越快,但通带不平坦度也越严重,经过仿真分析权衡,选取M=2,N=3。FIR滤波器阶数越高,性能越好,但耗费资源也越大,需要经过综合仿真分析确定。最终滤波抽取结果存入片内FIFO缓存,以统一速率传输至相关处理模块。

2.2.4 60通道采样信号时间同步

来自60部天线的信号,由于天线位置排列地点差异,导致太阳辐射传播和信号传输总距离不同,观测起始时刻模拟信号到达每个模/数转换器的时间不同步,这样每通道信号都需要做相应延时,使得信号在时间上尽可能精确对齐,以利于实时复相关处理。系统要求具有10 μs总延时和不大于1 ns延时精度。本文给出的同步方法分两步完成: 60个接收通道在同一绝对时刻开始采样,数据存入DDR?SDRAM缓存。信号采样时钟为1 GHz,即每个采样数据对应的时间间隔为1 ns,读取数据时,每个通道按照各自的延时长度计算出对应时刻数据地址,从这个地址开始读出数据混频滤波,这样实现了1 ns精度同步。如最大时延为10 μs,则对应舍弃前10 kb采样数据。通过可编程时钟延时芯片对采样时钟精确延时控制,可进一步提高延时调整精度。MC100EP196芯片最高输入时钟1.2 GHz,步进精度为10 ps,可在0~10 ns范围内精确控制时钟延时。A/D芯片复位,采样起始信号等和模/数转换相关信号也需要同时同精确延时,以保证信号之间时序同步。可选择两种方式确定每通道信号延时量:一种是系统初始化时,将每通道延时数据加载到FPGA中系统工作参数及模式控制寄存器中,根据这些参数来控制相关模块工作,保证各通道数据在时间上精确同步;另一种是每次测量间隔由系统总控制模块实时传输延时数据来控制时间同步,两种模式可根据系统需要随时切换。

3 仿真结果

采用Xilinx公司最新的Virtex?5高性能FPGA芯片XC5VLX155T为硬件实现平台进行仿真验证[9]。

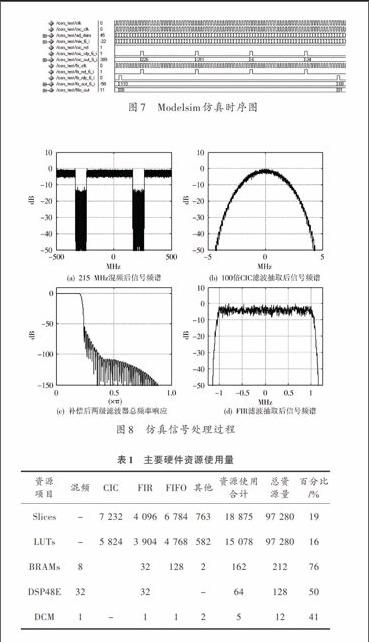

图7为第6通道I路信号混频与20×4=80倍滤波抽取Modelsim仿真时序图。选择主时钟频率为200 MHz,在15 ms内完成3 Mb数据处理量。混频乘法器直接调用FPGA内部集成的DSP48E数字信号处理单元完成[10]。第一级CIC滤波时钟同样为200 MHz,抽取率根据系统模式要求在20~100倍之间可变,同样输出数据周期相应改变。后续FIR滤波器抽取率为固定4倍抽取,工作时钟为200 MHz,输入数据速率选择CIC最大输出速率10 Mb/s,以便向下兼容8 Mb/s,6 Mb/s,4 Mb/s,2 Mb/s等更低输入速率。FIR工作时钟为输入速率为20倍,这样用于乘法运算的DSP48E内核可以充分时分复用,结合4倍抽取和滤波器系数对称等因素,一个DSP48E最大可实现151阶滤波运算。由于增加了辅助逻辑单元,限制了最大可执行速度,仿真结果表明不高于300 MHz,且需要占用1个Block?RAM(36×18 b)存储单元。使用CIC滤波器输出的RDY信号作为FIR滤波器输入ND使能信号,表示输入数据有效。

图7 Modelsim仿真时序图

图8为带宽400 MHz的线性调频信号叠加高斯白噪声作为仿真测试信号处理结果仿真图,通道中心频率为215 MHz、经过100×4=400倍抽取后获得带宽2 MHz信号,验证了方案的可行性,满足系统设计要求。

表1为主要硬件资源使用量,可以看出完成20~100倍可变倍数抽取的CIC滤波器资源占用量相对值较小、效率较高。FIR滤波器资源使用量相对适中,资源瓶颈是用于片内FIFO的Block?RAM,使用率最高,是芯片选型的主要考虑因素。仿真中实际需要FIFO最大容量为37.5K×2 b,由于生成FIFO的IP core工具只能选择2的整倍次幂,即只能选择65 536容量,每个FIFO占用了4个Block?RAM容量,每个子观测时间段可由3 ms延长至5 ms。如果增大抽取倍数,即不留过采样余量,则每个FIFO只需2个Block?RAM。总体分析可得出结论,如果选用资源量更大的Xilinx Vertex?5芯片或改变相应硬件工作参数、实现方式等因素,具有如下性能提升空间:单片FPGA具有同时观测400 MHz带宽内100个窄带频段信号潜力;通过增加本振存储数量,窄带观测频段中心频率可以固定间隔步进或增加DDS模块,产生任意频率本振信号;通过模式控制信号,可实时切换观测带宽、观测频段数等参数。

图8 仿真信号处理过程

表1 主要硬件资源使用量

[资源

项目\&混频\&CIC\&FIR\&FIFO\&其他\&资源使用合计\&总资

源量\&百分比

/%\&Slices\&-\&7 232\&4 096\&6 784\&763\&18 875\&97 280\&19\&LUTs\&-\&5 824\&3 904\&4 768\&582\&15 078\&97 280\&16\&BRAMs\&8\&\&32\&128\&2\&162\&212\&76\&DSP48E\&32\&\&32\&\&-\&64\&128\&50\&DCM\&1\&-\&1\&1\&2\&5\&12\&41\&]

4 结 语

射电观测系统要求采样频段宽,观测频点多且频率可变,带宽变化模式多且较窄,导致混频后滤波抽取因子变化范围达到100~400倍。本文研究了基于FPGA的模/数转换、高速缓存、混频、CIC与FIR级联抽取滤波等数字接收处理实现方法,满足系统功能和性能指标要求。提出一种简易的CIC滤波器补偿方法。采用可编程时钟延迟器件实现10 ps步进精度的时间同步性能。通过硬件编程仿真和实际开发板测试,验证了上述数字接收处理方法,硬件实现瓶颈为FPGA内部用于FIFO的存储资源,最后讨论了潜在的性能升级能力。

参考文献

[1] YAN Yi?hua, ZHANG Jian, HUANG Guang?li. On the Chinese spectral radioheliograph (CSRH) project in cm? and dm?wave range [C]// 2004 Asia?Pacific Radio Science Conference. Qingdao, China: [s.n.], 2004: 391?392.

[2] GARY D E, KELLER C U. Solar and space weather radiophysics: current status and future developments [M]. Berlin: Springer Publishing Company, 2004:54?61.

[3] 吴润泽,王宏祥,纪越峰,等.太阳射电频谱日像仪光纤传输技术分析与性能测试[J].天文研究与技术,2006,3(2):183?190.

[4] 高志成,肖先赐.宽带数字下变频的一种高效实现结构[J].电子与信息学报,2001,23(3):255?260.

[5] SUN Hong?wei, CHEN Jin?shu. A down?sample design under special condition in high?speed all?digital system [C]// Second International Symposium on Intelligent Information Technology Application (IITA apos 08). Shanghai, China: [s.n.], 2008, 3: 269?273.

[6] ABU?AL?SAUD W A, STUBER G L. Modified CIC filter for sample rate conversion in software radio systems [J]. IEEE Signal Processing Letters, 2003, 10(5): 152?154.

[7] DONADIO M. Lost knowledge refound: sharpened FIR filters [J]. IEEE Signal Processing Magazine, 2003, 20(5): 61?63.

[8] DOLECEK G J, MITRA S K. Simple method for compensation of CIC decimation filter [J]. Electronics Letters, 2008, 44(19): 1162?1163.

[9] DOLECEK G J,CARMONA J D.A new cascaded modified CIC: cosine decimation filter [C]// IEEE International Symposium on Circuits and Systems. [S.l.]: IEEE, 2005,4: 23?26.

[10] KWENTUS A Y, JIANG Z, WILLSON A N Jr. Application of filter sharpening to cascaded integrator ?comb decimation filters [J]. IEEE Transactions on Signal Processing, 1997, 45(2): 457?467.

[11] Xilinx Inc. Xilinx Virtex?5 data sheet [R]. San Jose, CA,USA: Xilinx, 2008.

[12] Xilinx Inc. Xilinx Virtex?5 Virtex?5 FPGA Xtreme DSP design considerations user guide [M]. San Jose, CA, USA: Xilinx, 2009: 72?73.

- 广东实验中学附属天河学校开展2020年秋季“开学第一课”活动

- 广东省教育厅关于2020-2021学年面向中小学生的全省性竞赛活动名单的公示

- 2020年秋季学期国家中小学学习资源全新上线

- 幼儿园区域活动中儿童行为的观察和评价

- 教师良好的行为品德

- 县域学前教育教研指导责任区的构建与运行初探

- 有效开展幼儿园数学活动的策略

- 基于思政课背景的职业素养课程案例使用策略

- 提高“贵生课堂”中小组合作的实效性

- 培养幼儿的分享意识与行为

- 让感恩伴随幼儿成长

- 徐闻县中小学教师心理健康教育“C证”培训圆满结束

- 创新方式|五华县联合粤教社率先在粤东地区启动“互联网+”普惠校内课后服务

- 如何培养小学生“说”数学的能力

- 《道德与法治》线上线下课程资源的融合使用

- 运用触摸感知手段进行少儿水墨画教学的研究

- 小学数学教学中有效整合多媒体教学的方法探究

- 立体、思考并举,活泼、深刻同存

- 略谈小学生初尝写作开篇

- 运用新媒体和传统手法,培养学生热爱学习的习惯

- 浅谈如何提升中学生英语阅读能力

- 信息技术环境下小学书法教学资源的开发与运用

- 汕头市学校开展秋季学期 学校疫情防控模拟演练

- 逐梦绿茵,羊城足球小将角逐最佳阵容

- 浅谈农村留守儿童心理特点及教育对策

- warehouseclub

- warehoused

- warehouseman

- warehousemen

- warehousereceipt

- warehouse receipt

- warehouses

- warehouse store

- warehousestore

- warehouse warrant

- warehousewarrant

- warehousing

- wares

- warfare

- warfarer

- warfares

- warfaring

- war film/war movie

- warful

- war game

- war-gamer

- war games

- warhead

- warheads

- warier

- 百年到老

- 百年后

- 百年大计

- 百年大计,教育为本

- 百年好事

- 百年好合

- 百年好和

- 百年孤独

- 百年富贵今谁见,一代功名托至公

- 百年强半

- 百年成事不足,一旦坏之有余

- 百年战争

- 百年松作柴烧——大材小用

- 百年松树,五月芭蕉——粗枝大叶

- 百年树人

- 百年歌

- 百年田地转三家

- 百年的大树

- 百年的歪脖子树

- 百年的歪脖子树——定型了

- 百年眷属三生定,千里姻缘一线牵

- 百年钻故纸

- 百年随手过,万事转头空

- 百废俱举

- 百废俱修