CFP MSA 100G光模块管理接口设计与实现

田园

摘要:CFP MSA定义了100G CFP/CFP2/CFP4光模块的硬件接口规范和管理接口规范。CFP MsA管理接口规范是CFP模块用户和CFP模块供应商之间的基础技术协议,用户对CFP光模块的管理即通过此协议实现。文章通过对比当前主流的2种CFP MDIO接口实现方案,从100G CFP光模块的成本、功耗以及技术演进的方向等因素综合考虑,提出一种100G CFPMDIO管理接口设计方案,并从软、硬件设计2个方面,结合CFP MsA规范,对此方案进行了详细的说明。本方案设计通过了严格的工程实验验证,应用此方案的100G CFP/CFP2光模块已经批量供应客户。

关键词:100GBASE-LR4;MDIO;CFP;MSA

IEEE 802.3ba 100GBASE-LR4标准制定了基于以太网应用的100G光模块光接口和高速电接口指标规范。CFP Multi-Source Agreement(MSA)定义了100G CFP/CFP2/CFP4光模块的硬件接口规范和管理接口规范。CFP MSA硬件规范对CFP光模块的高速收发数据信号、控制信号、告警信号、参考时钟、监控时钟、电源、地等作了规范定义,可用于指导100GCFP光模块的硬件设计。CFP MSA管理接口规范是CFP模块用户和CFP模块供应商之间的基础技术协议,用户对CFP光模块的管理即通过此协议实现。本文主要针对CFP MSA管理接口(MDIO)进行了深入研究,提出了一种CFP MSA管理接口(MDIO)实现方案,并实现其工程应用。

1CFP MSA管理接口设计

1.1 MDIO接口说明

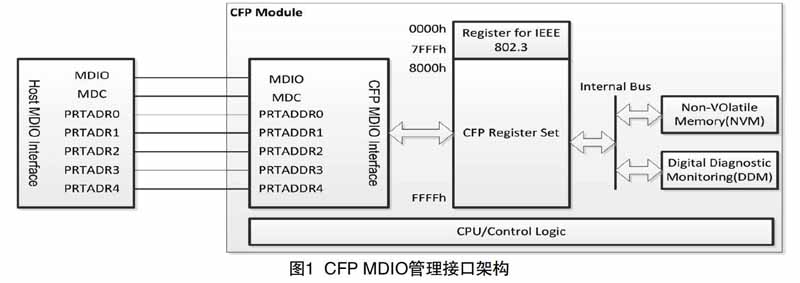

CFP管理接口是指HOST(用户设备)和100G CFP光模块之间的通讯/控制接口。MDIO总线是HOST与CFP模块间的通讯总线,MDIO接口包括MDC,MDIO,GLB ALRMn等5根地址线。CFP MSA定义MDIO接口遵守IEEE 802.3Clause 45标准,通讯速率4MHz且向下兼容到100kHz;MDIO读、写操作只在MDC时钟上升沿使能;支持MDIO器件地址选择,MDIO接口提供5根地址线支持最多32个可选地址(见图1)。

CFP寄存器以存储属性区分NVR非易失性存储器和VR易失性存储器2种。NVR寄存器标识模块属性(只读),在CFP光模块内部需要有非易失性存储设备支持数据存储。VR寄存器支持HOST对模块的控制命令和模块实时数字诊断信息更新。

1.2CFP MDIO接口硬件设计

CFP MDIO接口设计工程实现中通常有2种方案:方案一使用FPGA+MCU方式,FPGA编码实现从MDIO协议转换,FPGA和MCU之间定义私有接口,两者配合实现CFP模块标准管理接口功能;方案二使用MCU实现MDIO接口和模块管理功能。方案二使用单颗芯片,设计复杂度较方案一低,且功耗低,尺寸小,有成本优势。从第一代CFP模块发展到现在的CFP2和下一代的CFP4模块,对模块封装大小、功耗要求都更加严苛,在CFP2/CFP4的设计中方案二具有明显的优势。本文设计方案采用方案二。

本设计使用ARM Cortex-M3内核的ADuCM320微控制器作为CFP模块主控芯片,负责100G CFP光模块MDIO接口功能实现。MDIO接口区分主、从设备,接口间通讯只能由主MDIO设备发起,从MDIO设备被动响应,CFP模块MDIO实现从接口功能,用户设备(HOST)与CFP模块间的MDIO通讯协议遵守IEEE 802.3 Clause 45规范定义。CFP模块MDIO数据帧结构如表1所示。

MDIO数据帧长度64位(32位前导码+32位地址帧或命令帧)。IEEE802.3规定32位前导码为主机向从机发送连续32位逻辑“1”比特。sT是开始位(2bit),固定为OOb;OP是操作码(2bit);PHYADR是物理端口地址(5bit),地址值“b00000”为广播地址;DEVADD为MDIO器件地址(5bit),CFP模块对应PMA/PMD子层;TA为turnaronud码(2bit),读操作时为模块数据准备提供延时,写操作时为“b10”;16-bit ADDRESS/DATA为数据净荷,根据操作码OP的不同可以是寄存器地址或数据(16bit)。

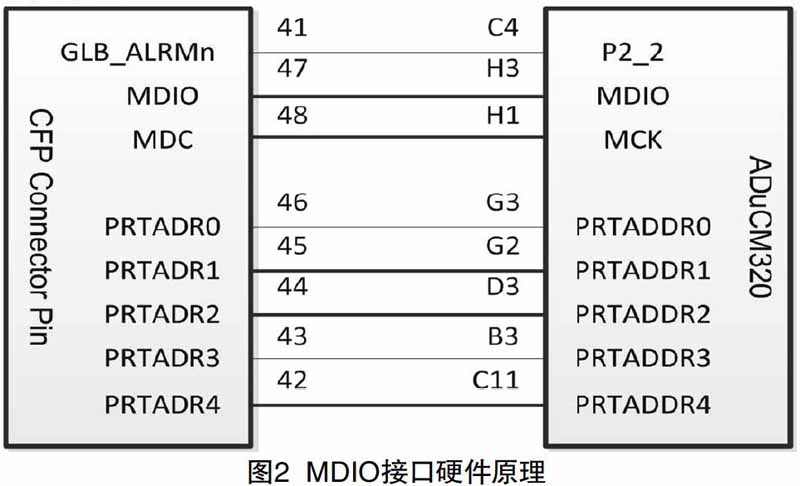

CFP模块内置MCU ADuCM320实现对MDIO数据帧的解析和处理。MCU MDIO功能引脚直接与CFP连接器相连,用户设备与模块的MDIO通讯通过连接器引脚,与模块内置MCU MDIO接口交互。CFP连接器是CFP模块与用户设备(HOST)连接的接插件,CFP MSA硬件协议对CFP连接器引脚功能做了定义。MCU与CFP模块连接器的硬件连接如图2所示。

1.3 CFP MDl0接口软件设计

本方案中软件需要编码驱动MCU MDIO从接口工作在4Mhz频率下接收和解析MDIO帧数据。MDIO帧数据有MDIO写操作、MDIO读操作、MDIO连读操作3种结构。用户设备Host发送给CFP模块的MDIO数据,模块MDIO接口通过获取帧数据中PHYADR。地址判断Host是否发起与自己的通讯,PHYADR地址由5位MDIO物理端口地址状态决定。若MDIO帧数据中的PHYADR地址与模块MDIO接口地址匹配,CFP模块根据OP操作码执行MDIO寄存器地址读写操作,否则CFP模块MDIO接口不对Host操作进行响应。

软件实现对CFP管理接口寄存器映射,图1CFP MDIO管理接口架构中标识的8000h~FFFFh地址寄存器,IEEE 802.3分配给100G CFP光模块使用,此部分寄存器根据存储属性分为非易失性存储器(NVR)和易失性存储器(VR)2种。

NVR寄存器从8000h~88FFh,模块在MCU片内Flash没有被代码空间填充的区域划分存储空间,存储NVR寄存器数据。使用MCU片内Flash可以节省用于存储非易失性数据的EEPROM芯片,降低模块功耗,节省成本。软件实现对MCU片内Flash的编程接口,在生产阶段写入NVR数据,Host读取NVR寄存器时,模块软件根据接收到的CFP寄存器地址,从NVR表中查找此寄存器地址映射的Flash地址,并读取数据写入MDIO接口buffer,等待Host读取。NVR寄存器对Host仅支持读操作。

2实验验证

验证本设计方案,选择NVR寄存器8000h执行读操作,CFP模块8000h寄存器为非易失存储,支持只读,协议定义此寄存器数值为0011h(CFP2);选择VR寄存器A011h的读写操作,A011h寄存器为易失存储,支持读写,其上电默认值为0200h。

8000h寄存器读读取数据为0011h;A011h寄存器读取数据为0200h。VR A011h寄存器写入0206h,读操作读取数据为0206h。

3结语

本方案设计实现的CFP MSA 100G光模块MDIO接口,已经完成工程验证,可以满足CFP MS艚理接口规范要求,成功应用于某公司100G CFP/CFP2光模块产品,且已经批量供应给客户。